如何利用GPS OEM来进行二次开发,产生高精度时钟发生器是一个研究的热点问题。在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS时钟发生器(GPS同步时钟)对维持系统正常运转有至关重要的意义。如在DVB-T单频网(S

关键字:

方案 技术 发生器 时钟 GPS

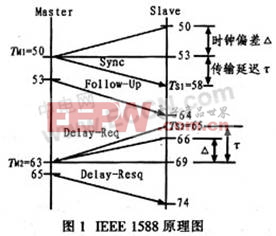

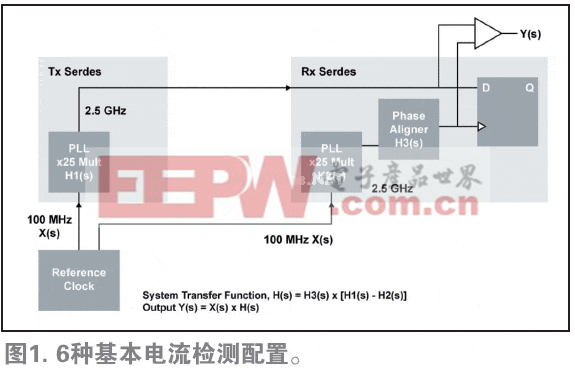

为实现分布式系统高精度同步数据采集及实时控制,提出一种基于IEEE 1588协议的分布式系统时钟同步方法。通过分析影响同步精度的因素,采用FPGA设计时间戳生成器,并且采用晶振频率补偿时钟解决时间戳的精确获取和从时钟相对主时钟的频率纠偏等问题。

关键字:

分布式 系统 应用 技术 同步 IEEE 时钟 基于 收发器

高性能模拟与混合信号IC领导厂商Silicon Laboratories (芯科实验室有限公司)今日发表在线时钟树设计服务,客户可利用此服务迅速获得Silicon Labs经验丰富的应用工程团队提供的定制化时钟架构建议,进一步简化设计、降低BOM材料成本,将开发风险降至最低。此外,Silicon Labs可提供业界最短的元器件交货期(约两星期或更短时间),从而大幅加速客户产品的上市时间。

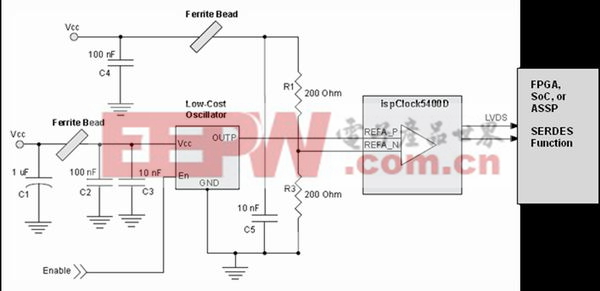

在强调性能的应用中,通常采用振荡器、时钟发生器和频率缓冲器的组合,为高速SerDes元器件、FPGA、处理器

关键字:

芯科实验室 时钟

针对X光安检机系统控制信号传输中采用传统串行通信方式所存在的问题,提出一种利用数字锁相环技术实现串行数据时钟提取的硬件解决方案。该设计基于FPGA进行开发,并针对安检机中串行控制数据传输的数字锁相环进行研究,设计了适用于FPGA的串行时钟提取系统,最终采用Verilog语言实现。该设计经过安检机系统的硬件平台实际测试,最终经过Signal TapⅡ读取实时数据进行验证,可以论证该方案的时钟捕捉周期短,捕捉精度也满足安检机系统要求,从而实现了安检机系统数字控制信号的单线路传输,有效地提高传输的可靠性。

关键字:

设计 实现 提取 时钟 控制 信号 安检 时钟提取

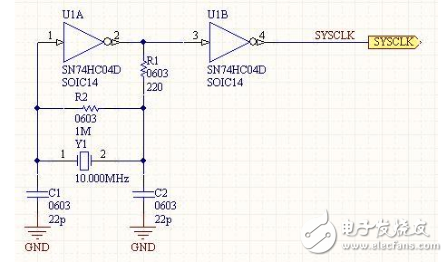

图3.23所示的电路,是一个16进制的反相器,用于产生30~160NS的延迟。每一级的延迟时间是5~35NS,具体数值由可变电阻的值决定。每一级的延迟时间不应该超过时钟周期的12%,以保重稳定工作。通过调整延迟级数(2或4)并

关键字:

时钟 简单电路 相位调整

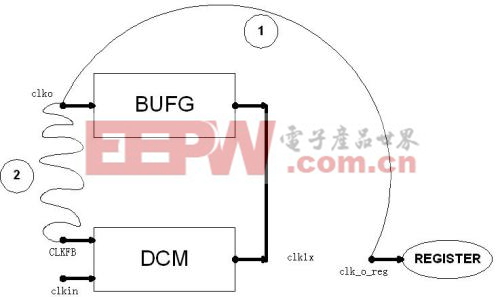

FPGA DCM时钟管理单元简介及原理,DCM概述

关键字:

简介 原理 单元 管理 DCM 时钟 FPGA

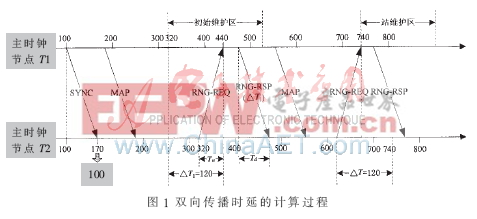

Ad hoc网络是一种特殊的无线移动通信系统,具有无中心、多跳等特点。结合无线传感器网络时钟同步协议RBS、TPSN和有线网络DOCSIS协议,提出了一种适合Ad hoc网络的时钟同步协议。先在Ad hoc网络上建立具有层次性的全网络结构后,以发送广播时钟同步信号的方式实现全网络节点的时钟相对同步,并通过周期性和突发性的双向测距实现和维护主从时钟节点之间精确的时间同步,以满足实际应用的要求。仿真实验表明,该时钟同步协议能满足不同时钟同步精度要求下的Ad hoc网络应用,具有低功耗和高可靠性的特点。 关键字:

时钟 同步 协议 测距 网络 Ad hoc 基于 通信协议

Analog Devices Inc.,全球领先的高性能信号处理解决方案供应商和数据转换技术领先者,最近推出两款时钟产品 AD9553和 ADCLK944。这些产品用于完整时序信号链中时,可提高同步光纤网络和无线基站的性能,并降低编程和设计复杂度。

时钟发生器 AD9553适合 GPON、SONET/SDH OC-48(同步光纤网络/同步数字体系)、测试和测量、数据采集、以太网、光纤通道、T1/E1、广播视频及其它无线和有线通信应用的低成本时钟转换需求。

ADCLK944旨在改善无线基站中

关键字:

ADI 时钟 数据转换 AD9553 ADCLK944

给出异步FIFO电路在高速数据采集系统中的应用,由FPGA生成独立时钟域的FIFO缓存器,采用FIFO的可编程设置参数启动数据传输,根据读写时钟频率异同的传输要求和FIFO的特性,采用一套控制电路,解决了可变速率数据缓存和固定时钟传输的问题。

关键字:

FIFO FPGA 时钟 201004

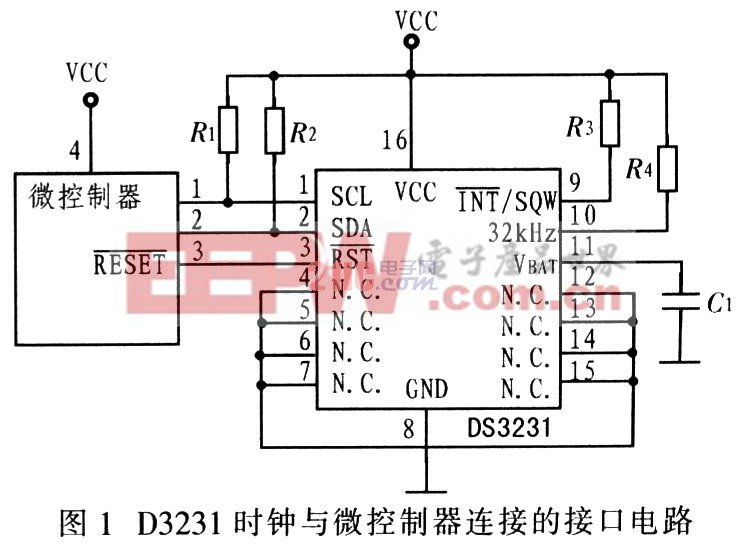

摘要:为避免电路系统在上电或断电后出现计时不准确的异常状况,提出采用高精度时钟芯片DS3231的解决方案。介绍DS3231的特点、工作原理以及引脚功能,设计其与微控制器进行通信时的软件、硬件接口,并给出相应的原理

关键字:

接口 设计 时钟 高精度 DS3231 基于

高速串行接口设计的高效时钟解决方案,数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架构。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线冲突、降低开关噪

关键字:

时钟 解决方案 高效 设计 串行 接口 高速

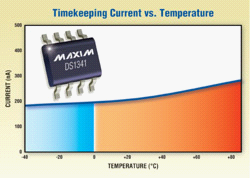

Maxim推出RTC (实时时钟)产品线的最新成员DS1341。该款RTC集成AGC (自动增益控制)电路,动态调节驱动电流,使器件正常工作时的电流损耗降至最低。此外,器件还支持高ESR晶体,为系统设计人员在晶体选择上提供了极大的灵活性。DS1341集节电和灵活的晶体选择特性于一体,非常适合用于医疗、销售终端机(POS)、汽车及便携设备。

器件的地址和数据可通过I²C串行接口访问,其它特性包括:两个定时闹钟、两路中断输出、一路可编程方波输出以及串行总线超时机制。时钟/日历提供秒、分钟、

关键字:

Maxim 时钟 DS1341 RTC

摘 要:为了保证管道输送的正常运行,对管道进行破坏预警监测具有极为重要的现实意义,快速、准确地判定事发地点是预警监测的重要内容。设计了管道预警监测及定位的系统方案,分析了其监测定位原理,并指出破坏声波

关键字:

GPS 时钟 定位

我们以一个实际的时钟电路来说明定时器的软件编程方法,时钟就是我们最为常见的显示时、分、秒为单位的计时工具,它是典型的应用代表。

关键字:

原理 电路 时钟 组成 AT89C2051

嵌入式系统的PCI Express时钟分配, PCI Express (PCIe)是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。然而,在嵌入式环境中,背板连接器引脚通常很昂贵。因此,采用点对点连接的星型结构的PCIe时钟分配方案就变得并不理想。本文将讨论如

关键字:

时钟 分配 Express PCI 系统 嵌入式

时钟介绍

时钟的概念多用于数字语音交换机,因为数字交换对于以时隙为单位的交换单位而言,其时间性的重要程度非常高。为保证交换机的正常工作,每套交换系统都必须配置精度极高的时钟发生器,用于交换系统内部工作。系统内部的时钟一般称为内时钟。

如果两套交换系统协调工作,那么必须要在两套系统之家,也就是两个内时钟之间进行协调,保证两个时钟同步工作,这就是时钟同步,对于每套系统的内时钟而言,另一套系统的内时钟即为外时钟 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473