X光安检机控制信号时钟提取的设计与实现

在安检机系统中,安检机的主设备与控制台的双向通信具有非对称性,由主设备X射线端采样得到的大量数据通过高速通道传送至PC控制台进行处理。然而由控制台传送给安检机的控制信号,因数据量较小,仅需低速通道进行传输即可,并且在安检主设备端对于高速数据的处理是基于FPGA平台实现的,若同时采用单片FPGA对接收控制信号进行处理,一方面可减少硬件电路的设计负担,另一方面也降低了设备成本。但与此同时,若该系统采用传统串行通信方式,则在处理高速数据的FPGA电路单元中引入低速时钟线,不仅容易受到电路板上高频信号的影响,而且由于控制台距离CT机距离较长,不利于时钟信号的传输。因此,对于安检机控制信号的传输一般采用单路串行低速通信方式。对于这种传输方式,在FPGA上采用一种高效的数字时钟提取技术就十分必要。

1 数字时钟提取环路基本原理

数字锁相环能让本地产生的时钟信号自动跟踪输入信号相位,从而实现一个闭环自动控制系统。数字锁相环的基本结构是由数字鉴相器(DPD)、数字环路滤波器(DLF)、数字可控振荡器(DCO)和本地时钟源(LC)组成的一个反馈环路,其具体原理框图如图1所示。

基于数字锁相环的数据时钟提取系统工作原理如下:本地产生一个高频率的时钟,数字鉴相器通过输入信号与估算时钟进行鉴相比较,输出鉴相信息。之后由数字环路滤波器根据鉴相信息对相位误差进行平滑运算,输出数控振荡器控制信号,通过对本地估算时钟的相位调整,最终跟踪到输入数据的位同步时钟。

2 各模块功能及实现原理

2.1 数字鉴相器

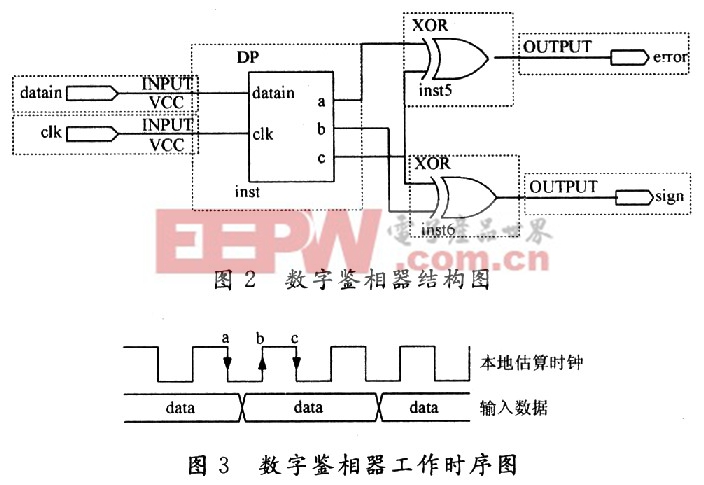

数字鉴相器用于获取输入信号与本地估算时钟的相位比较信息,常用异或门实现。在数字鉴相器中,首先将输入信号的正向过零脉冲与本地估算信号的正向过零脉冲进行比较,从中得到一个表明相位提前或延后误差的脉冲输出,其宽度反映超前(滞后)相位的多少。当本地估算信号超前于输入信号时,其输出为超前脉冲,反之,则为滞后脉冲。综合考虑到安检系统中的控制信号属于数字信号,并且由于FPGA的资源主要用于完成采集数据的处理,应尽量减少对FPGA资源的使用。本文的方案采用了超前/滞后数字鉴相器。

超前/滞后数字鉴相器硬件实现有两种方式,分为积分型结构与微分型结构。积分型结构的硬件实现比较复杂,但具有良好的抗干扰性能;微分型结构则具有相反特性。为了优化系统性能,选择使用微分型结构。尽管微分型结构的抗干扰能力较弱,但是结合安检机系统的实际环境,该结构可以满足系统需要。图2为微分型超前/滞后数字鉴相器的结构原理图,图3为其时序图。

评论