基于HyperLynx的高速PECL交流耦合时钟

引言

本文引用地址:https://www.eepw.com.cn/article/188363.htm随着电子技术的不断发展,数据的传输速度越来越快,高速时钟的应用日益广泛,如何保证时钟在高速跳变过程中的信号完整性、抖动、功耗等问题,已逐渐成为关注的问题。传统的时钟设计方法大多依靠经验和理论计算,但是随着时钟频率越来越高,时钟的电磁环境日趋复杂,时钟的传输线效应、过冲/欠冲、反射、振铃效应、趋肤效应都成为影响时钟设计的关键因素,只有使用现代科技手段,利用计算机的强大计算能力进行仿真才能够保证时钟电路设计成功。 HyperLynx是Mentor(Graphics开发的一款板级信号完整性的仿真工具。它可以进行损耗传输线的精确仿真,支持IBIS模型和HSPICE模型,可以使用过孔模型,允许多种激励源,可以分析信号的眼图、抖动以及EMC(电磁兼容性)辐射,用户界面简单直观。

在目前的高速时钟的电平标准中,PECL(正电压射极耦合逻辑)是应用较广泛的一种,绝大多数高速ADC(A/D转换器)、DAc(D/A转换器)器件都支持这一时钟电平。本文叙述。PECL的原理和常见端接方式,结合在ADc系统中的应用,使用HyperLynx工具对设计后的电路进行仿真以验证设计思想。

l PECL工作原理

PECL由EcL(射极耦合逻辑)标准发展而来,在PECL电路中省去了负电源,较EcL电路更便于使用。PECL信号的摆幅相对EcL要小,这使得该逻辑更适合于高速数据的串行或并行连接。

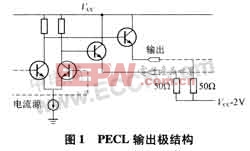

一个标准的PECL输出极如图1所示。

|

差分对管的射极通过电流源连接到地,差分对管驱动一对射随器以提供正、负输出。输出射随器工作在正电源范围内,其电流始终存在,这样有利于提高开关速度。LVPECL(低电压。PECL)输出极的标准输出负载是接50 Ω电阻至Vcc一2 V的电平,在这种负载条件下,由于射随器的基极一射极有0.7 V压降,故输出+与输出一的静态电平典型值为Vcc一1.3 V,0.7 V压降加在50 Ω终端电阻上的电流为14 mA,可知输出+与输出一电流为14 mA。PECL结构的输出阻抗典型值为4 Ω~5 Ω,表明它有很强的驱动能力。2时钟电路设计

下面根据具体应用进行设计。首先从时钟的发送端(输出)和接收端(输入)各自的特性着手进行设计。

2.1时钟输出结构

时钟输出端由时钟扇出芯片ICS853011的一对输出引脚担任。ICS853011是一款将任意差分时钟扇出为两路PEcL电平的时钟扇出芯片,其原理见图2。

|

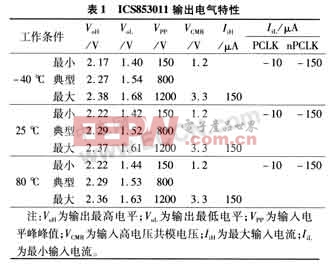

当其供电电压为3.3 V时,其输出电气特性如表l所示,输出高电平在2.295 V左右,输出低电平在1.52 V左右,输出峰峰值约为800 mV。

|

评论