自动反馈调节时钟恢复电路设计

0 引言

信息技术的迅猛发展使得人们对数据传输交换的速度要求越来越高,因此,各种高速接口总线规范应运而生,从USBl.1到USB3.0,从PATA到SATA,从PCI总线到PCI―Express,其接口总线速度也由最初的Kbyte发展到现在的上G比特。在传统的并行总线中,为了划分字节,通常采用时钟与多位数据并行传输的方式,这在当时数据率相对比较低的情况下,可以达到很好的效果,然而,随着数据传输率的越来越高,这种并行传输的方式遇到了难以克服的困难。这是由于存在着时钟畸变和路径延时,使得到达接收端的数据位之间的数据与时钟之间难以对齐,这样,接收方就很难正确地接收数据。为此,在高速数据传输领域,串行总线越来越显露出它的优势来。高速串行总线多采用嵌入式时钟来获得上G的带宽,并通过接收方的时钟恢复电路从接收的数据里恢复出同步时钟,实际应用中,通常有两种方法:

第一种是时钟数据恢复法,该方法是根据接收到的数据相位的变化来调整本地PLL或DLL电路的时钟输出相位,或根据本地时钟相位来调整接收到的数据的相位的方法来达到数据与时钟的同步,然后对数据进行l:1同步采样;

第二种是过采样技术,这种方法是在接收端用一个高速的时钟对输入数据进行过采样,一般来说,这个高速时钟的频率是原发送端时钟的3倍以上,这样过采样后的数据经过后继的数据处理电路就可以去除冗余的比特,从而恢复出实际需要的比特信息。

这两种方法各有优点和缺点,其中CDR方法由于不需要多倍于系统时钟的采样时钟,因而系统功耗比较小,数字电路逻辑比较简单,然而模拟模块设计复杂,数据同步所需时间比较长。相对于CDR来说,过采样技术数据恢复速度快,模拟电路设计简单,但是,数据后继处理电路相对复杂,功耗也较大。那么,有没有什么方法可以综合这两种方法的优点呢?本文提出了一种新的高速串行数据恢复方法。

1 系统设计

1.1 系统总体电路

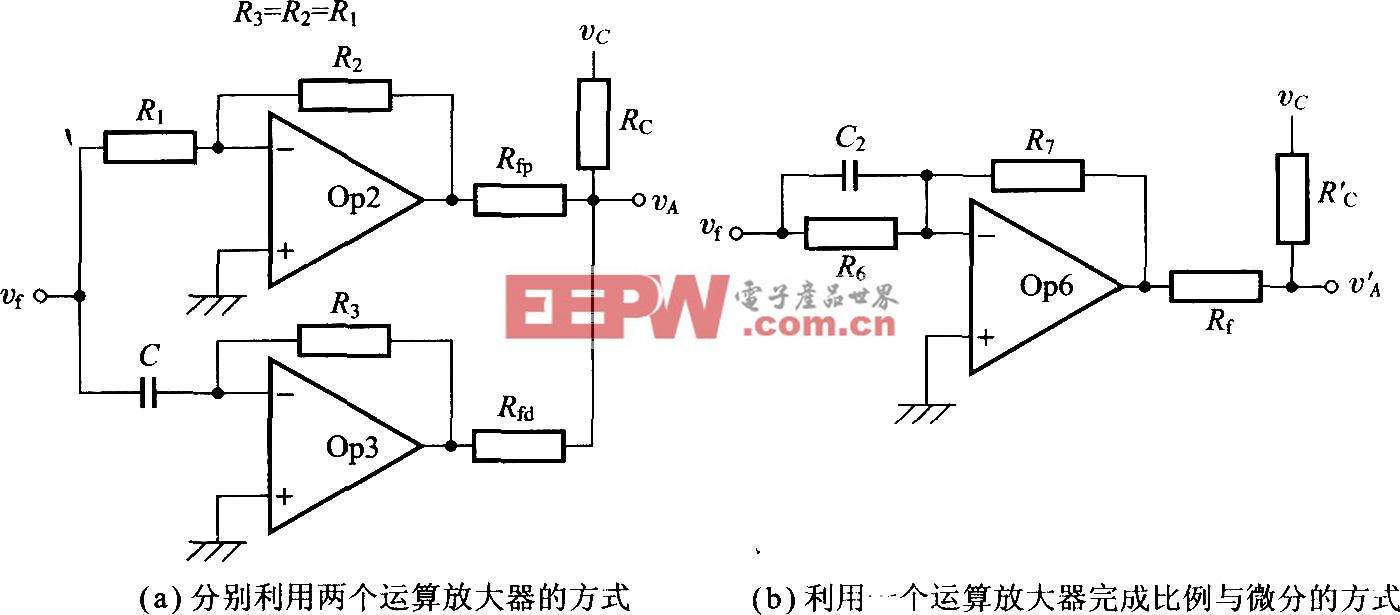

图1是一种新型高速串行数据恢复电路框图,此方法使用反馈通路来使本地时钟能快速锁定数据,该方法的抗干扰性尤其突出。

由于发生系统和接收系统的系统时钟间存在着误差,再加上传输通路上介质以及接收器本身的影响,使得信号的跳变沿存在严重的抖动和偏移,这样,接收端就必然需要一个本地时钟和异步数据同步的过程,本文采用的方法就是把输入信号通过PLL锁定延时器件的时延特性,将数据分为三路,每一路比上一路延时四分之一个时钟周期,然后使此三路信号分别被本地时钟采样并比较,以从中得出中路信号与本地时钟相位之间的延时是超前还是滞后,之后再将超前滞后信息经过译码逻辑变为一串8比特的控制信号给延时逻辑来调整时延,最终使数据与本地时钟同步。

评论