自动反馈调节时钟恢复电路设计

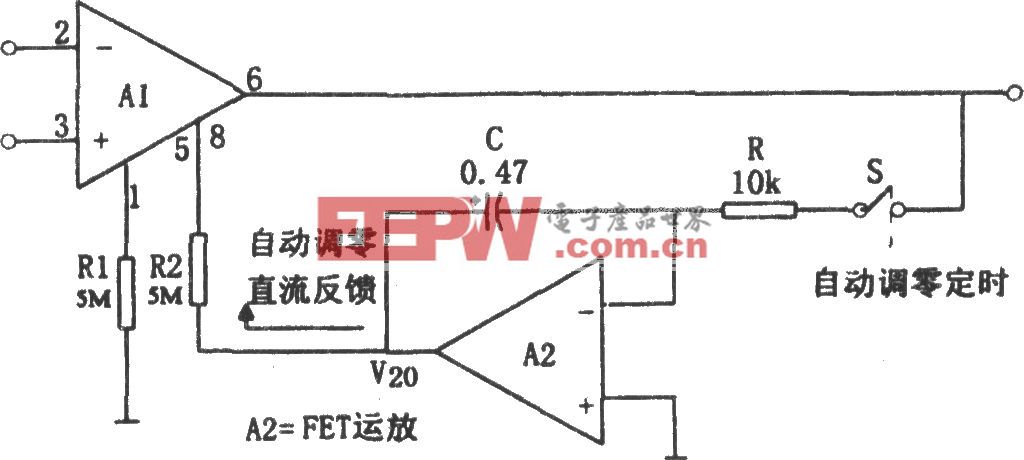

采样比较电路的时钟可由锁相环提供,其输入为延时逻辑电路的输出ssll、ssl4、ssl2等三路信号(如图5所示),时钟每隔一个周期对这三路信号采样一次并得到一组ss值,其中ss的值若为00l或110,则表示时钟相对于信号超前,此时超前指示信号early置高;若ss的值为011或100,则表示时钟相对于信号滞后,滞后指示信号delay置高;若ss的值为000或111,则表示时钟与信号同步。ss为010或101的情况则不会出现,在时钟的间隔周期内,early和delay标识都被置低。early和delay标识输出可给decoder模块进行后续处理。

1.4 相位译码电路

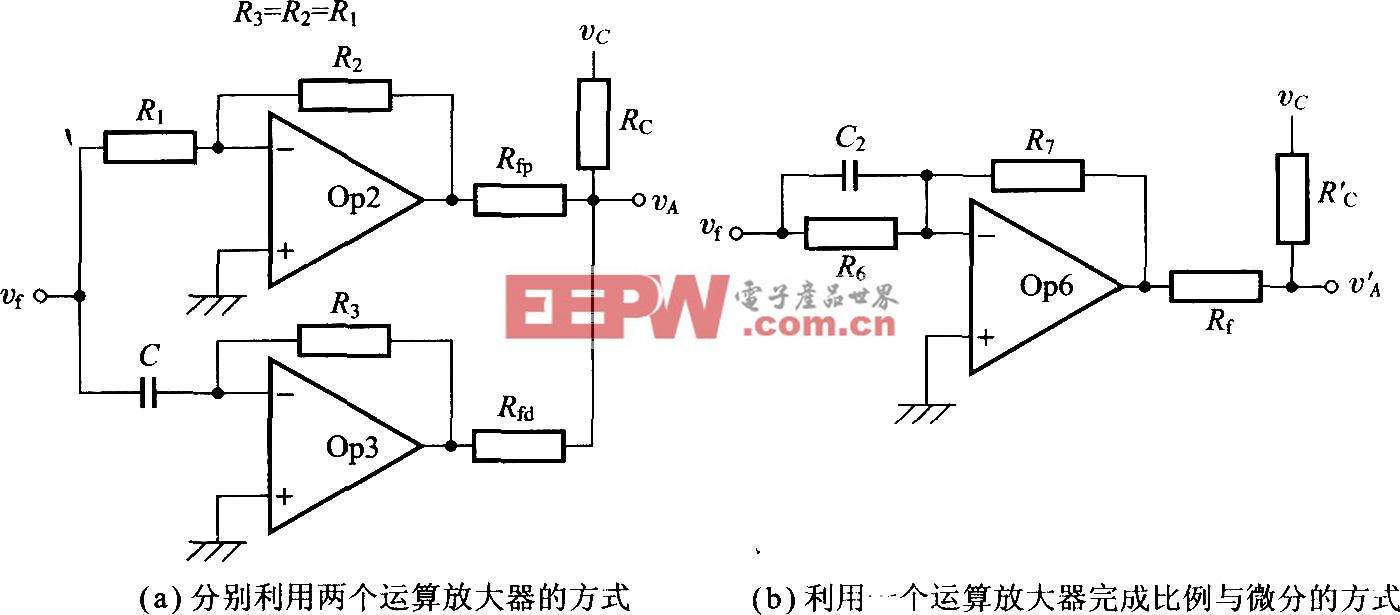

相位译码电路的核心部件是一个3比特的计数器,其计数器初始值为4,每当检测到early信号为高时,计数器减一;当检测到delay信号为低时,计数器加一;其它情况,计数器保持不变。然后便可对此计数器进行译码以得到一组8比特的控制字作为延时单元逻辑的输出。此后,经过反馈后的延时逻辑单元输出的ssl4信号将快速与锁相环锁定,并把同步后的信号和时钟作为CDR的输出送给后继逻辑。

本文引用地址:http://www.eepw.com.cn/article/152237.htm

2 仿真分析

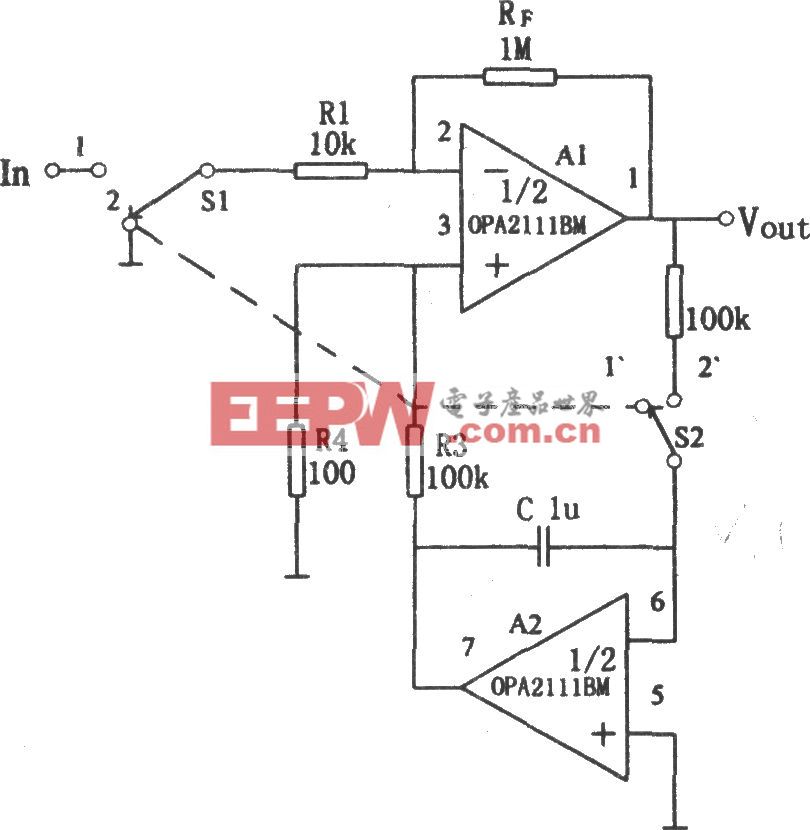

作者对该电路的设计进行了仿真分析,结果显示,在计数器s的初始值为4时,经过两次early的调节后,s变为2,此时的信号和时钟达到同步。经过多次以不同输入数据及不同输入数据的延时仿真证明,本方案能在小于8个系统时钟内达到同步。

3 结束语

本文提出了一个用于高速串行总线接口的时钟恢复电路,它采用改进的过采样技术,并配合已有的锁相环资源和反馈调节技术来实现信号与本地时钟的同步。该电路结构简单、面积小、功耗低,可用于USB2.0接口电路的设计中。芯片可采用中芯国际0.13纳米CMOS工艺投片生产。

评论