半导体C-V测量基础

强大的直流偏压导致衬底中的多数载流子在绝缘层界面附近累积。由于它们无法穿透绝缘层,因此当电荷积累在界面附近(即d为最小值)时电容在累积区达到最大值。如图1所示。从C-V累积测量可以得到的一个基本参数就是二氧化硅的厚度tox。

本文引用地址:http://www.eepw.com.cn/article/96649.htm当偏压降低时,多数载流子从氧化层界面被排斥开,耗尽区形成。当偏压反相时,电荷载流子远离氧化层达到最大距离,电容达到最小值(即d为最大值)。根据这时的反型区电容,可以推算出多数载流子的数量。这一基本原理同样适用于MOSFET晶体管,只是它们的物理结构和掺杂更加复杂。

在偏压扫过这三个区的过程中还可以得到多种其他参数,如图2所示。利用不同的交流信号频率可以得到其他细节信息。低频可以揭示所谓的准静态特征,而高频测试则可以表现出动态性能。这两类C-V测试通常都是需要的。

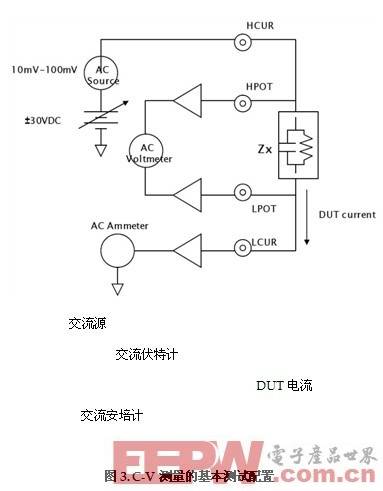

基本测试配置

图3给出了基本C-V测量配置的框图。由于C-V测量实际上是在交流频率下进行的,因此待测器件(DUT)的电容可以根据下列公式计算得到:

CDUT = IDUT / 2πfVac,其中

IDUT是流过DUT的交流电流幅值,

f是测试频率,

Vac是测得的交流电压的幅值和相角。

换而言之,这种测试通过加载交流电压然后测量产生的交流电流、交流电压和它们之间的阻抗相角,最终测出DUT的交流阻抗。

评论