嵌入式视频图像系统压缩算法的实现和优化

引言

本文引用地址:https://www.eepw.com.cn/article/92476.htm随着网络技术和多媒体技术的发展.视频通信的需求逐渐增加.同时最新的视频压缩标准不断推出。MPEG-4 ( Moving Pictures Expcrts Group-4)是国际运动图像像编码专家组(MPEG Moving Picture Experts Group)在1998年11月制定[1]的,它不同于其他标准.是个而向多媒体应用的压缩标准. 第1次提出了基于对象的压缩方法.使交互功能的实现成为可能。日前基于PC平台的MPEG-4视频编码器[2]在互联网的远程教育和高清晰电影等方面己经有较多的应用.但在硬盘录像机、多媒体通信等视频业务的嵌入式系统应用更为广泛。以DSP为嵌入式图像处理核心的系统,具有开发周期短,编程灵活的特点,因此DSP图像处理系统成为了研究热点。

DSPs结构特点

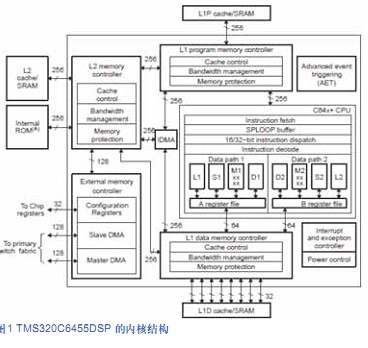

TMS320C6455是TI ( Tcxas Instrumcnts Incorporatcd)公司推出的最新高速DSP芯片[3]。具体结构见图1。最主要的特点从是结构[4]上采用了VLIW(VLIW: VeryLong Instruction Word)超长指令字内核结构.具有1200 MHz的CPU,每个周期可以同时执行8条32bit的指令。速度可达到9600 MIPS ( 1200 MHz X 8条指令=4 800 MIPS) 。片内采用2级高速缓存结构.片外存储器有很强大的外部存储器接口EMIF ( Extcrnal Mcm ory Intcrfacc)。 这些性能能满足视频图像处理的实时性要求.确立了它在高端多媒体应用中的地位。

图1 TMS320C6455DSP 的内核结构

对Cache的优化

最大程度地发挥Cache效率是达到期望编码器性能的一个关键因素[5]。Cache高速的存储访问速度可以减少CPU延迟周期.提高处理器的效率。TMS320C64xDSP有两级存储结构应用片内数据和程序存储。对于L1Cache能够以CPU的同样速度访问。L2Cache既可以作数据空间也可以作为程序空间使用.L2是片外空间与L1的桥梁。

MPEG-4视频编码器是以宏块为单位进行编码处理 ,只有当前宏块处理完成所有的过程后,视频编码器才能传送一个宏块。直接出现的缺点是: 一个视频编码器整个代码大于 L1P。每个宏块在 L1P和 L2之间的传送过程 ,导致严重的Cache缺失。而一个单独的宏块从片外存储空间到片内空间的搬移 , 也不能发挥 EDMA (Extended Direct Memony Access )的优势。

评论