一种动力调谐陀螺脉冲力反馈及脉冲计数系统设计

动力调谐陀螺是一种利用挠性支承陀螺转子,并将陀螺转子与驱动电机隔开,其挠性支撑的弹性刚度是由支撑其本身产生的动力效应来补偿的。他广泛应用于导弹、坦克、火箭、航天器、导航与定位等领域,是陀螺技术发展史上具有重大革新和突破的第三代惯性级精密陀螺。本文将介绍该陀螺的力反馈电路及其脉冲记数电路的实现方法。

本文引用地址:https://www.eepw.com.cn/article/87848.htm1 系统的硬件设计

硬件包含两部分:动力调谐陀螺(DTG)脉冲力反馈系统设计和基于SOPC的数据采集部分设计。

1.1 动力调谐陀螺(DTG)脉冲力反馈系统设计

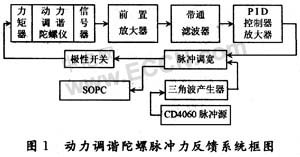

系统结构框图如图1所示。动力调谐陀螺,力矩器和信号器在硬件结构上是集成为一体的。

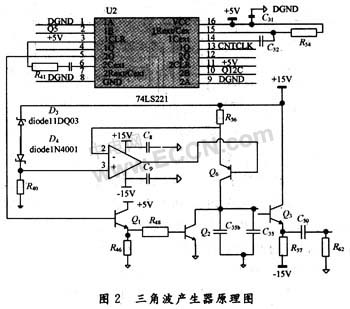

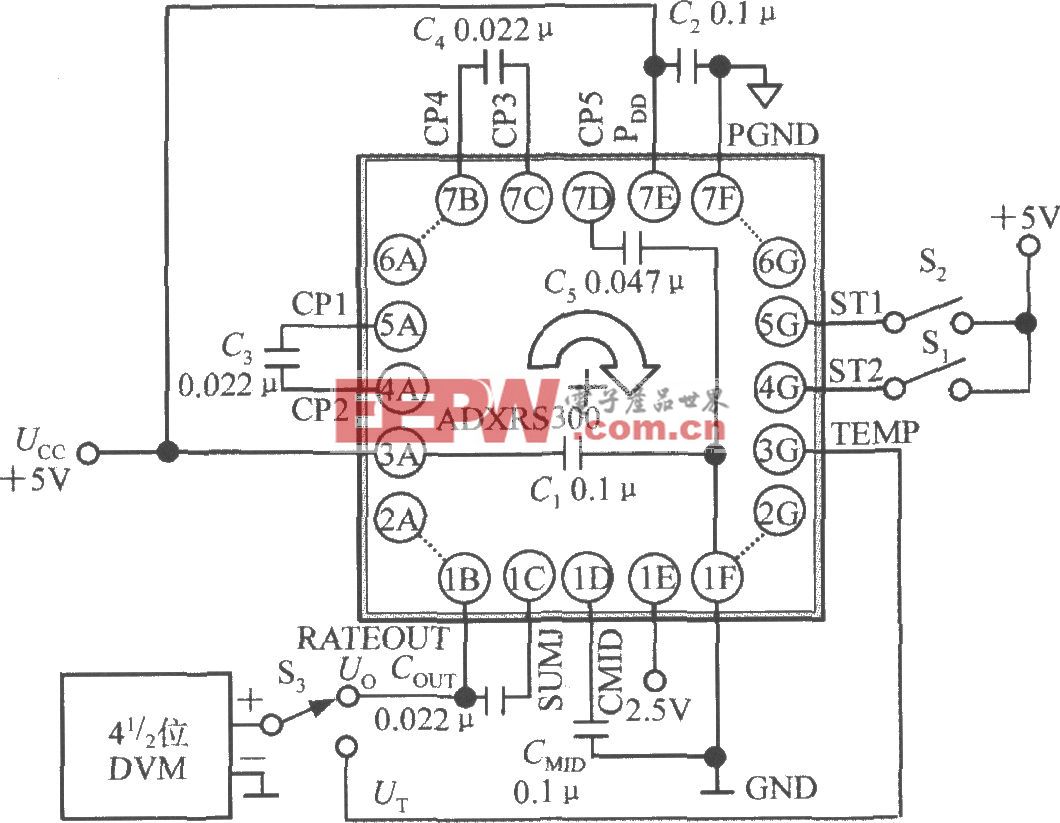

利用力反馈回路实现对动力调谐陀螺的锁定,由陀螺漂移及输入角速率产生相应信号器输出控制陀螺仪力矩器中主线圈中模拟电流的大小,信号器输出经过前置放大,滤波和PID校正后送到脉冲调宽电路,与产生的三角波进行合成。陀螺正转时,三角波脉冲宽度增加;陀螺反转时,三角波脉冲宽度减少。通过测量正负通道的脉冲数量来测得陀螺的转速和转向。以下重点介绍三角波产生电路,其原理图如图2所示。

三角波产生器采用双电源±15 V供电,2Q端口输出的是CD4060脉冲源产生的5分频正脉冲信号,由于Q1接成射集跟随器形式,经三级管Q1射集产生的是同步脉冲信号,其输入三级管Q2的基集,高电平时Q2导通电容充电,低电平截止时电容放电。电容反复充放电产生三角波,其周期与时钟脉冲周期相同。放大器提供稳定电压参考值,PNP型复合管Q6与放大器组成恒流源对电容充电。Q3也接成射集跟随器,射集输出与时钟脉冲信号同步的三角波信号,经过RC积分电路产生具有正负脉冲形式的三角波信号。将陀螺输出信号经过放大、滤波、教正后与三角波比较,从而产生调宽波控制极性开关给力矩器加电流。

1.2 SOPC系统的设计

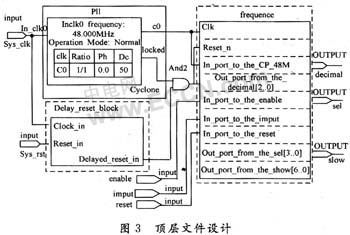

SOPC系统实现对陀螺力反馈脉冲数的采集。SOPC(System on a Programmable Chip,片上可编程系统)是Altera公司推出的一种灵活、高效的解决方案。Altera公司的QuartusⅡ软件提供了可编程片上系统(SOPC)的一个综合开发环境,是进行SOPC设计的基础。QuartuSⅡ支持图形界面设计和硬件描述语言VHDL设计,受文章篇幅限制和便于描述,原有的VHDL设计都已转换为bsf格式,即可被工程文件直接调用的图形符号。首先,在QuartusⅡ中创立工程文件,应用QuartusⅡ集成的SOPCBuilder开发工具创建嵌入式处理器内核NIOS系统,指定目标FPGA和时钟周期,然后添加到工程文件中。NiosⅡ嵌入式处理器包含三种内核:经济的(NiosⅡ/e)、标准的(NiosⅡ/s)和快速的(NiosⅡ/f)内核,每种都针对不同的性能范围和成本。使用A1tera的QuartusⅡ软件、SOPC Builder工具和NiosⅡ集成开发环境IDE,用户可轻松地将NiosⅡ处理器嵌入到他们的系统中。Nios内核处理器及外围电路的设计如图3所示。

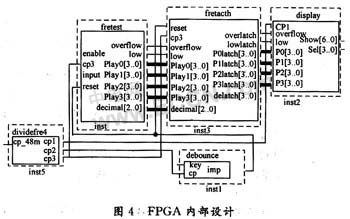

顶层文件设计了一个SDRAM时钟系统和复位电路,该时钟信号由FPGA内部PLL的来产生,可利用FPGA内部的PLL来产生一个内部时钟信号,作为NiosⅡ处理器和分频器的时钟输入。该系统设计了一个2 kB片内ROM存储器(Onchip_ROM)用于存储器代码以及程序运行空间;1 kB片内RAM(Onchip_RAM)用于变量存储(R/W数据)、Heap、stack等。FPGA内部其实没有专用的ROM硬件资源,实现ROM的思想是RAM赋初值,并保持该初值,即是只读的。ROM的内容在FPGA进行配置时一起写入FPGA。添加的PIO外设包括时钟信号(CP 48M)、使能信号(enable)、复位信号(reset)、七段码驱动信号(show)、片选信号(sel)、小数点显示信号(decimal) 等。FPGA内部设计如图4所示,共5个下层模块:分频模块(dividedfre4)、防抖模块(debounce)、计数模块(fretest)、锁存模块(frelatch)、显示模块(display)。这5个下层模块组成一个上层模块。

2 软件部分设计

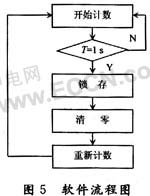

2.1 软件流程图

软件流程图如图5所示。

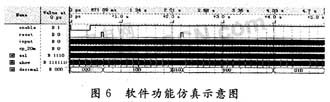

2.2 软件功能仿真

Altera公司的QuartusⅡ软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。QuartusⅡ集成开发环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证和仿真。利用QuartusⅡ进行的功能仿真结果如图6所示。

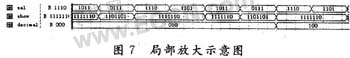

图6中输入被测频率信号input=20 kHz,由局部放大图可知,t=1 s时,闸门信号开启,t=2 s时,锁存计数值,显示为20.00 kHz。局部放大如图7所示。

3 结 语

由试验仿真结果与实际电路中测的数据完全吻合,证明系统设计成功。而前提是动力调谐陀螺运行稳定,所以陀螺脉冲力反馈系统是设计中的重要环节。三角波产生电路是脉冲力反馈回路的核心和硬件调试环节中最需要重视的部分。

评论