一种高速波控系统的设计

1 引 言

本文引用地址:https://www.eepw.com.cn/article/87847.htm相控阵是通过波控系统控制阵列天线各单元通道的相位、幅度以形成空间波束并控制其方位角和俯仰角。早期的波控系统一般采用硬件电路来实现,这种实现方法的缺点是设备量大,不灵活,很难实现波束的复杂计算,不易满足特殊要求。后来采用单片机、DSP芯片来设计波控系统,单片机通常不计算波控码,仅仅是根据接收到的波控码布相,而DSP可以自己计算波控码,但是单片机、DSP都是象流水线一样串行的运行指令,也就是说,不能并行地对各天线单元通道进行波控码计算和布相。

针对波控系统要求高速计算、多通道并行逻辑控制的特点,选取FPGA作为波控系统的核心处理器。目前采用大规模FPGA器件来实现波控系统的设计还很少,采用FPGA能够大大简化波控系统硬件设计,把以前的硬件逻辑控制电路全部集成在FPGA芯片内部,从而实现对波控羁的高速并行计算和对各单元通道的并行同步控制,本文针对这种基于FPGA波控系统设计方案的可行性进行了探讨。

2 波控系统设计要求

2.1 接口设计

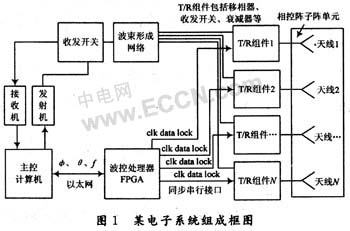

某电子系统组成如图1所示。系统主控计算机和波控系统之间信息交换量很大,要求收发速度都要很快;同时天线阵元很多,接口必须有可扩展性,实际中采用了以太网(Ethernet)技术。

以太网协议是指根据IEEE 802.3规范制定的局域网协议(Local Area Network,LAN)中的CSMA/CD协议。一方面,以太网与传统的RS 485、CAN总线等相比,以太网更加高速、通用,经过适当剪裁和优化的TCP/IP协议栈,也完全可以适应工业用途的需要。另一方面,相对于新兴的USB 2.0,IEEE1394等总线,以太网技术在传输距离、布线成本以及控制软件的通用性上都有明显的优势。

波控系统需要实时控制T/R组件以及进行状态检测,采用同步串行传输方式,时钟20 MHz,完成一次T/R组件重新布相以及状态检测需要1μs。

2.2 模块化设计

系统天线阵列有几百个阵元,并且要求可扩展性,用一个FPGA波控板不可能实现这样复杂的控制和运算,每一个阵元在天线阵的位置是不一样的,但是对T/R组件、移相器的控制以及接口都是相同的。每个FPGA波控板控制一个天线子阵,而一个天线子阵由25个天线单元组成,所以考虑采用模块化设计方法。系统上电工作,主控计算机立即将每个FPGA波控板的位置信息下发。波控板也根据自己所接受到的位置信息计算每个天线阵元的移相值。这样的设计就实现了波控板的互换性,每一个波控板的软件和硬件都是完全相同的,任何一块出了问题都可以立即更换,而不需要考虑他的位置,方便维修工作。

3 波控系统设计

3.1 波控码计算公式

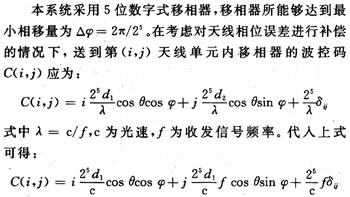

相控阵天线上第(i,j)单元通道相对于参考单元第(0,0)单元通道的相位差φ(i,j):

![]()

式中:d1为相邻天线单元在阵面水平方向的间距,d2为相邻天线单元在阵面垂直方向的间距;(φ,θ)为天线波束指向,其中φ为方位角,天线波束与天线阵面水平方向的夹角,θ为俯仰角,天线波束与相控阵阵面的夹角;δij为第(i,j)单元通道与参考单元之间的初始相位误差。

3.2 FPGA实现

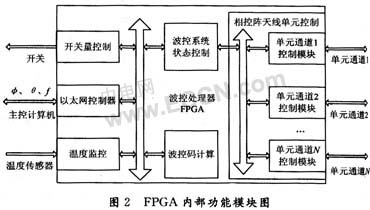

FPGA作为波控系统的核心处理器,按照功能划分为:波控码计算模块、以太网控制器模块、相控阵单元控制模块、温度控制模块、开关量控制模块、系统状态控制模块。FPGA内部各功能模块划分如图2所示。这些模块都是并行工作,比如相控阵天线单元控制模块可以对各单元同步实时控制,完全保证各单元通道相位同步切换。

波控码计算模块将得到的波束指向信息(方位角、俯仰角)和频率快速的计算出相控阵各单元通道的相位值。为了获得相控阵天线的低副瓣性能,必须严格控制天线各单元通道内的幅度和相位误差。同时,T/R组件、天线单元在加工安装过程中各单元通道并不能够保证相位完全一致,存在相位误差。因而,在测量各天线单元与参考天线单元之间的幅度和相位误差的基础上,波控码计算模块通过改变波控码,对各单元通道之间的相位误差加以修正。

以太网控制器模块主要实现以太网接口设计,使波控系统能够和主控计算机高速可靠的进行信息交流,主控计算机下发频率、方位、俯仰信息,波控系统上传实际波束方位俯仰角、T/R组件状态、工作频率、温度等信息。

相控阵单元控制模块的任务就是并行同步控制各单元通道,先将移相值和收发开关控制值组合成波控码,然后通过自定义的I/O口将波控码发送到相应的T/R组件,实现对T/R组件的控制,完成布相,得到需要的波束指向。

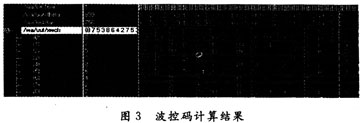

FPGA各功能模块软件设计均采用VHDL语言,VHDL语言用硬件数字逻辑电路来实现软件算法,他的特点是实现整数的加减法、乘法非常便捷,但是实现除法(被除数不是2的整数次幂)和对小数的算法比较困难。按照上面公式计算波控码,VHDL语言直接实现这样的计算是很困难的,他不能够直接实现三角函数运算和浮点运算。解决方法就是,在FPGA的配置芯片中存储一个4 096×16 b的正弦表,通过查表法间接实现三角运算,浮点运算则采用定点运算来替代。用仿真软件ModelSim XE对方位俯仰电扫描计算结果进行仿真,波控码计算结果如图3所示。

3.3 波控系统设计验证

在波控码实时计算软件设计中,所有的加减乘除都采用定点运算,而且三角函数计算也是采用查表法实现,所以和浮点计算相比波控码计算结果误差加大,精度降低。选取离参考单元较远的第(4,4)单元通道,将浮点运算和定点运算得到的波控码值进行比较,波控码误差δcode:

用Matlab模拟FPGA定点运算和三角查表运算进行仿真,在仿真图中可以清楚地看到波控码误差绝对值小于0.02,定点计算结果和真值误差很小。

同时通过系统实际运行来验证方案的可行性,将波控系统与系统联试,FPGA在每次重新布相后将各个移相器的波控码上发给主控计算机,将这些波控码与主控计算机浮点运算结果相对比,发现实际情况与仿真结果相吻合,实际运算与仿真运算一致,符合精度要求和实时性要求。

4 结语

本文阐述了一种基于FPGA实现相控阵波控系统的设计方案,并且通过软件仿真和实际运行验证这种方案设计的可行性。这种方案设计充分发挥了FPGA芯片的高速、并行特点,可以同步并行控制天线各单元通道,保证了相控阵天线波束切换的高速性和各单元的一致性。

绝对值编码器相关文章:绝对值编码器原理

评论