80C51原始IP核内部RAM的扩展方案

引 言

本文引用地址:https://www.eepw.com.cn/article/82699.htm80C51系列单片机是一类经典的8位微处理器,其设计方法和体系结构一直是其他各类单片机设计的参考典范,自从20世纪80年代面世以后,得到了极大的发展与应用。直到今天,市场上还有一大部分单片机应用成品将其作为处理核心。基于80C51系列单片机无知识产权保护、市场应用广泛等优点,对其进行功能拓展,既有利于经济上节约成本,也有利于成果的推广使用。而随着单片机应用日趋复杂化,传统的51系列单片机在设计上的不足逐渐显现出来。如在现有128字节内部RAM基础上,处理一些比较复杂的算法就显不足。鉴于此,本文在Oreg-ano公司设计的8051 IP核(即下述MC8051)基础上,进行了对其内部RAM高128字节扩展。给出一种新的扩展设计方法,实现了对与一般RAM区地址空间相连的高128字节的间接寻址操作,并以此为基础,对内部RAM进行了可达64 KB的扩展实现,通过了相应的软硬件仿真测试。

1 对MC8051高位128字节的扩展设计

对MC8051高位128字节的扩展设计主要分3个方面加以说明:一是传统80C51系列的内部基本结构;二是高128字节的寻址方式;三是对IP核内部的RAM地址选择控制。

1.1 传统80C51系列的内部基本结构

80C51是经典的单片机系列,具有典型的单片机体系结构,由CPU系统、ROM、RAM、I/O口以及特殊功能寄存器SFR、2个16位定时/计数器、5个中断源和1个串口组成。针对本文所要讨论的内容,这里介绍一下80C51存储结构和寻址方式:80C51系列单片机存储器结构采用哈佛型结构,物理上共分片内外程序存储器、片内外数据存储器4个存储空间。对于数据存储器,片内外数据存储器地址彼此独立,指令寻址各自不同,这里主要关注片内数据存储单元的结构。

8051单片机共有7种寻址方式,这里只对其中3种作一下简要介绍:立即寻址,操作码后的一个字节就是实际操作数本身;寄存器寻址,操作码后为某一寄存器编号,寄存器的内容为操作数;寄存器间接寻址,其与寄存器寻址的区别在于前者寄存器中的内容就是操作数,而后者寄存器中的内容为操作数地址,此地址指向的寄存器中存入的数据才是实际操作数本身。

1.2 高128字节的寻址方式

由前面介绍内容可知,MC8051内部RAM分为地址相连、功能不同的两部分:低128字节的内部用户RAM区和高128字节的特殊功能寄存器区(SFR)。这两部分均可用寄存器直接、间接寻址方式进行寻址操作。经过设计修改的8051,低128字节的功能和操作方式完全不变,对其高128字节,分为地址重叠和功能不同的两部分,以不同的寻址方式加以区别,控制操作。高128字节如果作为内部用户RAM使用,只可以通过寄存器R0、R1进行寻址,以地址为85H的寄存器单元为例,若此时85H作为SFR,则用命令“MOV 85H,#33H”;若此时作为一般内部用户RAM单元,则用命令:

MOV R0,#85H

MOV @R0,#33H

在MC8051中,寄存器R0、R1只应用于寄存器间接寻址使用,即R0、R1中存储的内容为间接寻址中操作数的地址。对高128地址空间,如果作为一般的RAM寄存区使用,只采用间接寻址;如果作为特殊功能寄存器区(SFR),则采取除间接寻址外的其他寻址方式。这样就可以通过只对.R0、R1中内容进行条件判定,确定是否触发对高128地址空间进行一般RAM数据操作。

1.3 IP核内部的RAM地址选择控制

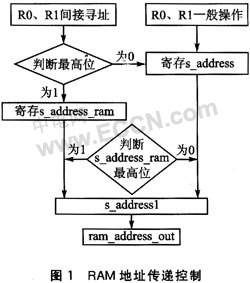

在MC8051中,对低128字节用户RAM区的读写有专门的地址输出ram_address_out。由于1个字节的寻址长度为256,所以ram_addreSS_out只取内部地址s_adr低7位,即ram_address_out<=s_adr(6 downto 0),辅以RAM写使能控制,实现对低128字节的读写。这里由于要对RAM区扩展成为256字节,所以用户RAM区的地址应该可以寻址256字节长度。这就要求对IP核中对RAM区的地址传递有相应的修改,修改后地址的具体传递过程如图1所示。

一个完整的执行过程如下所述:首先CPU从ROM读取指令,然后到内部状态机进行指令解释,送入译码器执行具体的数据和地址的存取操作(译码器中通过地址多路选择器adr__mux和数据多路选择器data_mux来实现对地址和数据的控制)。如果此时命令不涉及寄存器间接寻址,由图1可知,取到的RAM地址就是一般8051的执行结果。如果此时进行寄存器间接寻址,则可分为两种情况:一是对高128字节的间接寻址,此时的操作目的,是要对高128字节进行一般RAM的数据操作;二是除第一种情况外的一般寄存器间接寻址操作。由于SFR不能使用寄存器间接寻址,所以这两种情况可以根据R0、R1中存储的地址的最高位进行判别。

第一种情况:最高位为“1”时,说明高128字节(80H~FFH)作为一般RAM来使用,此时把R0、R1中的地址赋给RAM地址,同时置RAM使能控制ram_write_en为“1”,实现对某一高位地址的写操作。还以85H为例,执行指令“MOVR0,#85H”,R0中内容变为85H,然后执行“MOV @R0,#33H”,此时R0用作间接寄存器,进行间接寻址,且寄存器中的字节最高位为“1”,对RAM区操作的地址就是间接寄存器中寄存的地址85H,从而实现对85H的数据存储。

第二种情况:最高位为“0”时,说明只是对低128字节进行间接寻址操作,执行过程如一般8051。

2 64 KB内部RAM的扩展设计

通过对一个特殊移存器(选取84H,记为SRAM0)的软件配置,在高128字节内部RAM扩展设计的基础上,可以实现内部64 KB RAM的扩展。在对高128字节内部RAM的扩展设计中,通过对s_address_ram最高位进行判断,确定地址信号s_address1,进而作为内部RAM地址ram_address_out输出。以这个方法为基础,将ram_address_out改为16位长,SRAM0中内容与s_address1的值并置作为ram_address_out输出,即ram_address_out<=SRAM0&s_address1,可以实现对内部RAM 64 KB的扩展。此时对数据进行存取时,每次对84H赋值后,CPU对数据进行存取,对64 KB内部RAM的寻址,就相当于以SRAM0为页地址指针,以256字节为页深度进行页面寻址操作。相比较于以XRAM作为数据存储区,本设计有两个优势:其一,除SRAM0中为全0的情况,其余地址空间均可直接寻址,而XRAM地址空间只能间接寻址,在进行大量数据反复存储调用时,可以缩短代码长度,有效提高执行速度;其二,由于内部数据传输指令MOV大多为单指令周期指令,而外部数据传输指令MOVX全部是双指令周期指令,所以在进行大量数据存取时,执行速度会有较大提高。

3 软硬件仿真测试

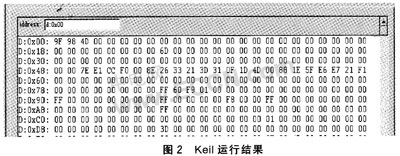

采用由Model技术公司开发的ModelSim SE 6.0进行功能仿真,利用Keil公司的Keil uVision2编写51汇编测试程序,编译产生可执行文件载入ROM进行功能测试,最终的仿真结果与Keil uVision2中编译执行结果相对照,验证设计功能的正确性。对设计的测试采取黑盒测试法,测试程序是已有的一些比较复杂的算法,如DES、AES。以DES为例,明密文存取、密钥生成、中间值暂存和结果都放在高128字节来处理,仅用到低128字节区的可位寻址区,密文地址空间为90H~97H,明文地址空间为98H~9FH,明文数据为38H、33H、32H、37H、31H、34H、32H、33H,密钥地址空间为80H~87H,密钥数据为00H、31H、31H、33H、34H、35H、36H、07H,最后将80H~87H和90H~97H地址空间中的数据结果送入地址空间48H~5FH中,如图2所示。

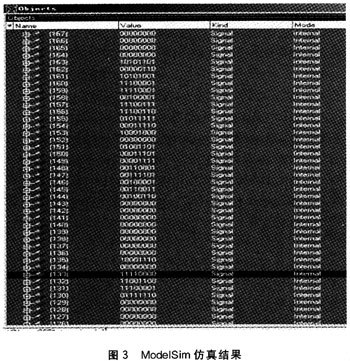

将二进制.dua可执行文件载入ROM,使用ModelSim对其进行功能仿真,结果如图3所示。

两方结果对照:128~135这8个高位寄存数为:00H、00H、7EH、E1H、CCH、F0H、00H、8EH,144~159这16个高位寄存数为:26H、33H、21H、3DH、31H、0FH、1DH、 4DH、00H、88H、1EH、5FH、E6H、E7H、21H、F1H,图中的160~163位,是用于暂存32位圈子密钥的,这里不作详细介绍,通过对照可知结果正确。硬件实现采用Altera公司的CycloneII系列的EP2C35F672C6器件作为设计载体,在QuartusII 5.0下对系统进行编译综合下载,使用RS232串口,在每次复位时,对RAM的明文和初始密钥进行重新配置,利用串口输出验证结果。实验结果均正确。

结 语

针对8051现有的RAM内部数据缓存不能满足实际应用要求的现况,本文给出了一种新的对内部RAM高128字节的扩展实现方案,并以此为基础,对内部RAM进行了64 KB的扩展设计;通过了相应的软、硬件仿真测试,验证了设计的正确性。

tcp/ip相关文章:tcp/ip是什么

评论