FPGA在语音存储与回放系统中的应用

1 引言

本文引用地址:https://www.eepw.com.cn/article/80373.htm随着数字信号处理器、超大规模集成电路的高速发展,语音记录技术已从模拟录音阶段过渡到数字录音阶段。在数字化录音技术中,压缩后的语音数据有些存储在硬盘中,有些存储在带有掉电保护功能的RAM或FLASH存储器中。笔者介绍的语音存储与回放系统,未使用专用的语音处理芯片,不需要扩展接口电路,只利用FPGA作为核心控制器,就能完成语音信号的数字化处理,即实现语音的存储与回放。

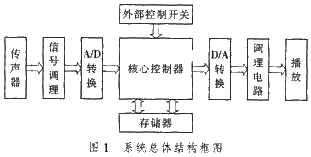

2 系统总体结构

数字化语音存储与回放系统的基本工作原理是将模拟语音信号通过模数转换器(A/D)转换成数字信号,再通过控制器控制存储在存储器中;回放时,由FPGA控制将数据从存储器中读出,然后通过数模转换器(D/A)转换成模拟信号,经放大后由扬声器输出。本设计方案系统总体结构框图如图1所示。

3 各部分电路设计

3.1 音频前置放大器

声音通过传声器转换成微弱的电信号(mV级),必须进行放大才能经A/D转换送入单片机。可采用专用的音频前置放大器。本系统采用频带宽、噪声低、失真小的NE5534芯片,如图2所示。

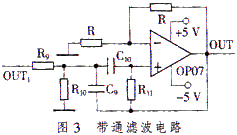

3.2 带通滤波器(BPF)

本系统选用有源带通滤波器,由运算放大器OP07组成。其中心频率f0=1 kHz,通带为300 Hz~3.4 kHz。如图3所示。

3.3 A/D转换器

带通滤波器的输出信号经采样保持(LF398)后送A/D转换电路进行抽样和量化,将模拟信号转换成8 bit数字信号。本系统选用AD7820芯片。

AD7820有2种工作模式,由MODE决定:当MODE接高电平时芯片工作在WR模式下;当接低电平时工作在RD模式下。本系统将芯片设置在WR模式的S-A方式(最简单的方式)下,即:MODE接高电平,RD和CS持续接低电平。当WR变低时开始转换,在WR上升沿的700 ns后,转换数据被输出。

本系统采样频率fs=250 kHz,字长8 bit。 AD7820为高速、微型、单通道A/D转换器,采用逐次比较技术,转换时间1.36μs,转换范围0~5 V,使用单电源+5 V供电。逐次比较使用31个比较器,1个高4位ADC和1个低4位ADC,输入信号被抽样电路追踪和保持;有专门ADC输出接口设计,可与任何端口连接而不需要接口路基电路。所有的数字信号输出使用锁存与三态缓冲电路,使其可直接与微处理器的数据总线和系统的输入端口相连接。

3.4 D/A转换器

语音回放需将存储的数字信号通过D/A转换器转换成语音模拟信号。本系统选用DAC0808,其为8 bitD/A集成电路芯片,满量程输出需要150 ns,用±5 V电压供电时功耗仅有33 mW。

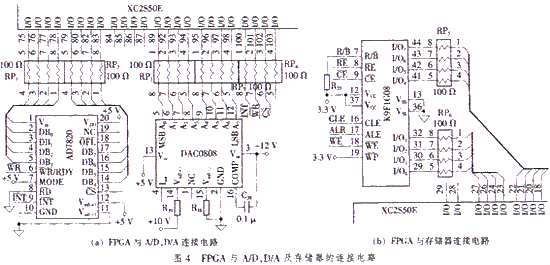

3.5 FPGA及存储器

在一个以FPGA为核心的语音处理系统中,用存储容量、存储时间、回放音质等指标衡量语音处理系统优越性。系统选用FLASH作片外存储器,实现语音数据的数字录音和回放,既保证了系统的高性能,又降低了系统成本。三星公司产品K9F1G08UOM具有128 M×8 bit(1 Gbit)存储容量,采用NAND闪存技术工艺,工作电压2.7~3.6 V,功耗低,容量大,数据访问速度高。

此芯片由8 192个块(block)组成,每块由32个页(page)组成,每页为512×8 bit。如果需要进行字节级访问,128 Mbyte容量需要27根地址线,所以需要4个周期的地址输入,依次是列地址(A0~A7)、低位行地址(A9~A13)、高位行地址(A14~A26),其中A8由00h和01h2种命令分别设置为低和高,以分别选择每页的前256Byte和后256Byte。如此设计I/O总线目的为:(1)减少芯片的管脚数量;(2)当系统需要更大容量的芯片时,可维持系统板级设计的一致性。

系统的A/D采样速率设置在250 kHz左右,字长8 bit,1 s的语音数据需要8 Kbyte的存储空间,而存储器容量为128 Mbyte,所以1片可存储9 min左右的语音数据。FPGA与A/D,D/A及存储器的连接如图4所示。

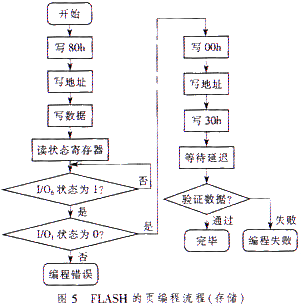

4 软件设计

在录音按键有效时,首先对FLASH 中的1 024进行块擦除,然后对FLASH进行写操作,此时才能往存储器中写数据,FLASH的页编程流程图如图5所示。

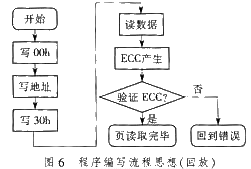

放音状态有一个主要的程序即对FLASH的对操作,图6为程序编写流程图,其中ECC为误差纠正代码。另外,程序中通过控制RE的低电平信号频率来控制输出数据的速率,实际程序中把频率控制在250 kHz左右,与A/D的采样频率相同。

5 结束语

系统电路简单,程序简洁。采用FLASH存储器保存语音数据,即使断电仍能保持数据不丢失,保存数据安全可靠。如果在软件中增加数据压缩算法,可节省存储空间,是一种实用的电路设计方案。

评论