一种延迟电路在变频控制中的应用

摘 要:本文主要介绍一个由RC和或门电路组成的延迟电路在一变频控制中的应用,解决了原有芯片死区时间不确定的问题。

关键词:延迟电路;IPM;死区时间

变频控制死区时间简介

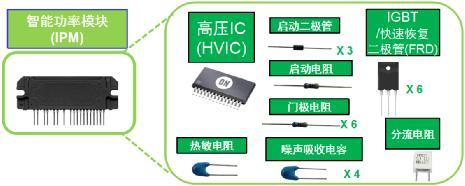

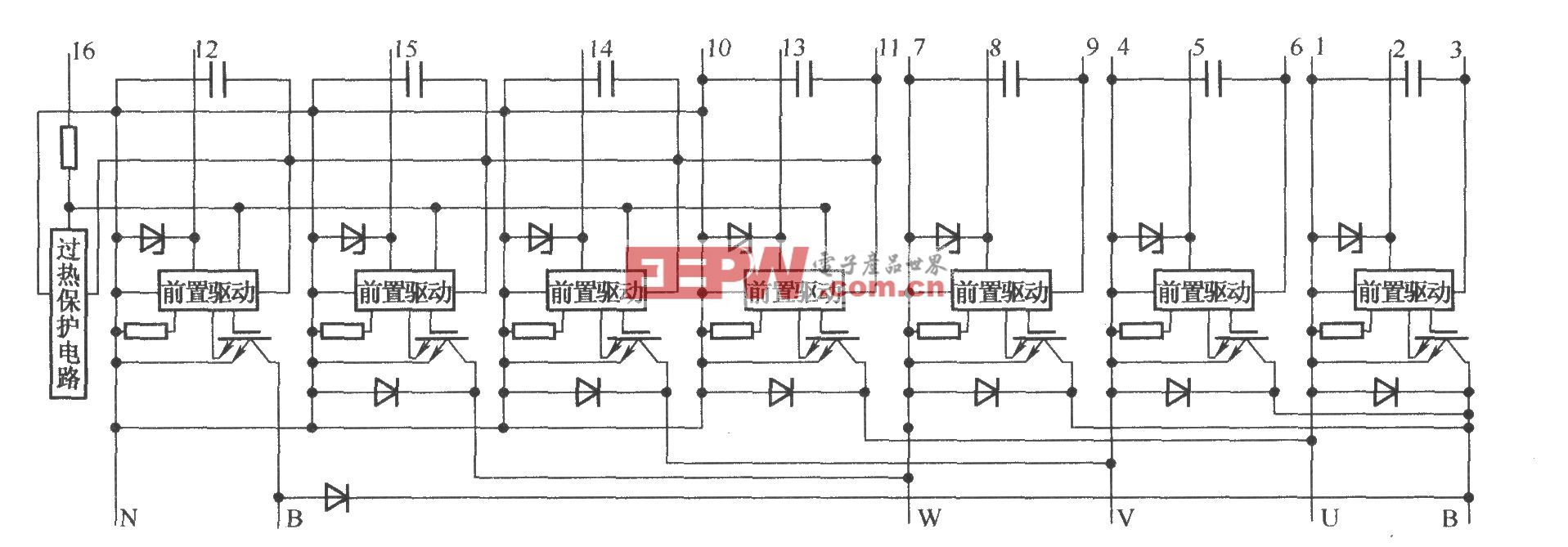

熟悉IPM(Inteligent Power Module)工作原理的工程师都知道,控制IPM工作的六路PWM信号,在导通时序上,控制同一通道的上下两路信号不能出现同时导通的情况,如图1所示。也就是说同一桥臂的两个IGBT不能同时导通,如果同时导通,轻则引起IPM的工作保护,造成停机,重则将IPM模块击穿,造成模块损坏。所以,在PWM信号的算法实现上,同一通道的上下两臂的控制信号在导通时间上要有一个时间间隔,即“死区时间”。不同的模块对死区时间的要求是不一样的,如三菱采用分离电源供电的IPM 模块,其死区时间通常要求在3.5ms以上,而采用单电源供电的模块,其死区时间则可以做到2ms。通常,死区时间的数值可以在EEPROM中设置,表1即为本文所用模块死区时间的设置表。

问题的出现及解决方案设想

在实际工作中会碰到这么一种情况,由于硬件掩膜的问题,造成了芯片上电后0、1状态的不确定,除非EEPROM中设置为0,否则死区时间都是不确定的,从而使得模块的可靠性大大降低。由于批次掩膜的数量多达数万片,如果解决不了这个问题,则会造成很大的损失。为了有效地降低成本,必须想办法把这批有缺陷的芯片利用起来。综合各方面的考虑,要解决这一问题,本文提出了三种解决方案:

1. 增加一个芯片作为变频驱动,原芯片作为主芯片。

2. 不增加单片机,选择一款高速IPM,然后在EEPROM中设置一种理论上合理的死区时间,如2.4ms&19.2ms,由于芯片上电后0、1状态的不确定,所以还需要通过实验来进一步验证:

a. 如果死区时间为2.4ms时IPM没问题;

b. 如果死区时间为19.2ms时压机电压不存在问题。

则说明理论上该方案可行。

3. EEPROM中死区时间设置为0,然后增加一硬件延迟电路,对PWM控制信号的下降沿进行延迟拖后(信号低电平有效),上升沿不变,从而实现对死区时间的调节。

分析三种方案,第一种方案明显地会增加产品的成本,第二种方案理论上可行,不过实验上比较复杂,压频曲线难以确定,且会使产品的可靠性降低。第三种方案,由于要求只对信号下降沿进行延迟拖后,考虑到RC加一或门电路可以实现这一功能,如果增加这种延迟电路,成本增加不多,实验上比较简单,且还能使该芯片通用化,可行性好。下面就介绍该电路的实现方案。

实验方案的实现及实验结果

图2为其中一路控制信号的原理图。MCU输出信号(X)经由设计的延迟电路延迟后(X)输入到IPM模块。由于EEPROM中的死区时间设置为0,所以,如果不加外围电路,则PWM信号的死区时间为0.5ms,远不能满足模块的工作条件,要保证IPM 正常工作,必须使信号延迟大于模块能够工作的最小死区时间。为了保证模块能够安全可靠地工作,这里选择的外围延迟时间为10ms,故电阻参数为1KW,精度为1%,电容为103pF,误差为10%。经实际测试,电路实际效果如图3(a)、图3(b)所示。

图3(a)为信号有延迟和无延迟的信号比较,其中3通道为有延迟的信号波形,2为无延迟的信号波形。从示波器上能够明显地看出3通道的信号下降沿有明显的拖后,经测量,这个拖后时间为10ms左右。图3(b)为同一桥臂的两路信号经延迟后的波形,从波形可以看出,在2通道导通之前,3通道已经关断,而3通道则是在2通道关断以后才导通,保证了两路信号之间稳定的死区时间。当然,波形上显示这个死区时间并不是严格的10ms,但这个误差是在允许范围之内的,(下面会对此进行分析)。采用该电路后,压缩机运行平稳,且满足产品所要求的性能。

实验误差分析

考虑到延迟电路中电阻、电容的误差,最大延迟误差可以很容易地计算出:

上偏差:

ms

下偏差:

ms

由计算出来的结果可以看出,对于10ms的死区时间来说,该误差是完全可以接受的。

结语

综上所述,利用外围所加的一个简单的延迟电路,成功克服了芯片上的硬件缺陷,取得了显著的经济效益。■

参考文献

1 [美]S.M.欣内尔斯著. 现代控制系统理论及应用. 第2版. 李育才译. 北京: 机械工业出版社,1979

2 清华大学电子学教研组编. 模拟电子技术基础简明教程. 第1版. 高等教育出版社,1995

3 张燕宾著. SPWM变频调速应用技术. 第2版. 机械工业出版社,2002

评论