用FPGA来加速采用OpenCL的多功能打印机图像处理

在高性能计算、娱乐和科学计算市场,OpenCL的采用在持续增长。OpenCL的灵活性和便携性使之成为了一个开发图像处理应用的优秀平台。然而,OpenCL尚未应用到硬拷贝打印机和多功能打印机(MFP)市场。传统上,打印机/MFP市场使用全定制系统级芯片(SoC或ASIC)、专用集成电路进行图像处理。在本文中,我们探讨了配合Altera SoC FPGA(现场可编程门阵列)的OpenCL在核心MFP图像处理流水线中的应用。核心图像处理流水线以每分钟大于90页信纸大小的全色RGB持续速率运行,图像分辨率为600DPI(每英寸点数),同时采用了成本有效的FPGA器件。相比运行在嵌入式CPU上的基于C语言的软件流水线,OpenCL流水线可实现至少40倍的性能提升,在高端台式CPU上的运行改善了5倍。

本文引用地址:https://www.eepw.com.cn/article/271266.htmI.引言

历史上,MFP和打印机厂商都是开发定制ASIC或SoC器件来执行图像处理操作。这些ASIC/SoC器件包括图像流水线,用以接受来自CCD或CIS传感器的RGB数据,执行滤波、缩小/放大、色彩空间转换、图像分割和半色调操作。然后,由此产生的经处理的图像使用减色着色剂进行打印:青色、品红、黄色和黑色。其目标是在打印副本上精确地再现原始文档,而不引入视觉假像。

在底层技术(如DDR内存和USB连接)变得过时之前,ASIC/SoC器件通常有三年的有限寿命。随着硅技术的不断萎缩,开发一个定制ASIC/SoC所需的投资在继续增加。一个采用双核处理器、必要的连接、DDR3内存控制器、图像处理、GPU、LCD控制器等的28纳米SoC的设计、开发和交付需要花费超过1000万美元的成本。

取决于许多因素,大型SoC/ASIC器件的开发周期要花18至30个月,包括新IP的数量和大小、利用以往设计的能力、设计团队经验和成熟的有针对性的硅技术。

打印机/MFP市场的产品周期是24到36个月的时间。打印机/MFP市场成长速度平缓,增加了以较低成本和较短开发周期提供更多功能的竞争压力[1].

随着ASIC/SoC开发周期接近同一时间MFP产品的生命周期,MFP/打印机厂商需要一个新的平台来缩短开发和部署周期。基于SoC的OpenCL和FPGA的组合为解决这一难题提供了一个有趣的解决方案。

II. MFP图像处理流水线背景

一个重要的研究机构已经在文档图像处理领域积累了近20年的经验[2][3].大部分早期工作都侧重于图像处理的基础知识,包括提供统一色彩的校准输入传感器数据、去除来自传感器噪声的滤波,实现图像尺寸缩小或放大的缩放算法,以及实现使用二进制像素打印连续色调图像数据的半色调。当前的文档图像处理研究和开发处于图像分析、内容提取和数据压缩技术领域。[4][5][6]

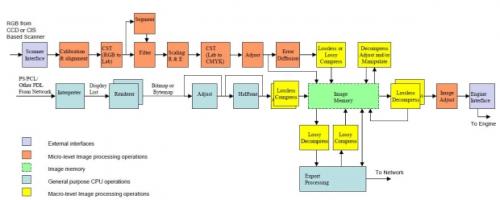

所有MFP文档图像处理产品都可执行一系列基本功能——复印、扫描和打印。图1用图形说明了一台个MFP设备的基本功能或流水线。复印和扫描的操作相类似,开始于从一个扫描设备到设备无关的彩色空间的原始RGB数据转换。复印操作进一步处理设备无关的色彩空间图像,并创建用于打印的CMYK图像。扫描操作在设备无关的色彩空间图像上执行一组不同的图像处理操作。这些操作可以包括:图像分析、用不同频率内容将图像分割为多个图像层、OCR、光学字符识别和数据压缩。然后,所产生的图像转被移到任一本地存储介质,如USB闪存驱动器或网络设备。

图1:简化的MFP图像处理流水线

图字:

来自CCD或基于CIS扫描仪的RGB;分割

扫描仪接口;校准和调整;CST(RGB到Lab);滤波器;缩放R E;CST(Lab到CMYK);调整;误差扩散;无损或有损压缩;解压缩调整和/或操作

来自网络的PS/PCL/其他PDL;解译;显示列表;渲染器;位图或字节图;调整;半色调;无损压缩;图像存储;无损解压缩;图像调整;引擎接口

有损解压缩;有损压缩;至引擎

出口处理;至网络

外部接口;微观图像处理操作;图像存储;通用CPU操作;宏观图像处理操作

打印功能接收一个采用PDL(页面描述语言)的编码,或图形显示接口格式的文件。在采用PDL文件的情况下,MFP设备必须首先解释文档语言,并创建一个原始对象列表。渲染器捕获这些对象,并将其转换成数字CMYK位图/位图图像。所产生的数字图像可被进一步处理和随意压缩。GDI打印机不需要解释过程,因为传送到打印机的图像是一个显示对象的列表。

一旦打印或复印流水线创建了CMYK位图/位图图像,图像即被发送到引擎在所需介质上打印。

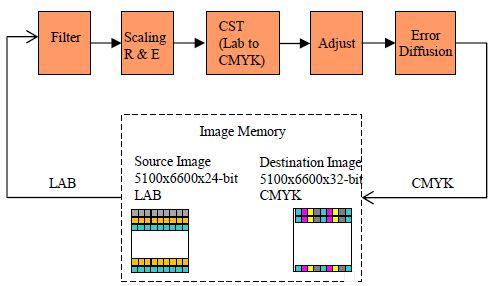

本文的重点是一个OpenCL MFP核心复印流水线(CCP)的开发,如图2所示。

图2:核心复印流水线

图字:

滤波器;缩放R E;CST(Lab到CMYK);调整;误差扩散

图像存储

源图像5100x6600x24位LAB;目标图像5100x6600x32位CMYK

III. MFP核心复印流水线

CCP由5个内核组成:7×7滤波器;用pad/crop缩放或减小与放大;色彩空间转换;调整和误差扩散。我们将简要地回顾各个算法和相关的内存需求。

A. 7×7滤波器

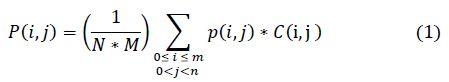

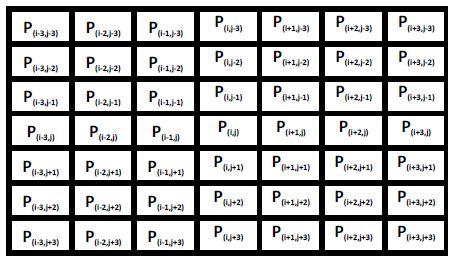

7×7滤波器是一个2D对称滤波器,可降低图像噪声。它的每一行需要跨连续7行乘连续7个像素的49个像素的上下文(context)。MFP应用通常使用一组系数来实现一个平均或锐化滤波器。7×7滤波器的一般形式是:

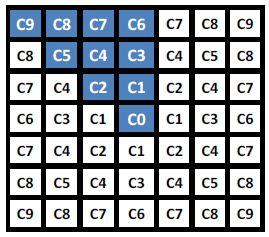

图3示出了该系数阵列和输入像素阵列。系数C0 - C9足以定义一个7×7滤波器。

7×7系数阵列

7×7输入像素阵列

图3:7×7系数和输入滤波器阵列

由于系数值经常重复,滤波处理可以避免重复的乘法和加法。相反,乘以相同系数的像素可首先加入,然后与滤波器系数相乘一次。图4直观地显示了潜在的优化。这个数字仅为了清晰起见,并不代表OpenCL设计。

图4:滤波器工作矩阵

fpga相关文章:fpga是什么

三维扫描仪相关文章:三维扫描仪原理

评论