【从零开始走进FPGA】对立统一——异步时钟同步化

一、什么是对立统一

本文引用地址:https://www.eepw.com.cn/article/269614.htm什么是CEO,就是首席执行官,是在一个企业中负责日常经营管理的最高级管理人员,又称作行政总裁,或最高执行长或大班。

那么,在FPGA系统,需不需要一个最高级别的执行官,来管理所有进程呢?为了系统的有序性,不至于凌乱、崩溃,答案必然是肯定的。

谁都知道,FPGA内部时序逻辑的工作,是通过时钟的配合来完成任务的。那么当系统中有异步时钟的时候,怎么办?每一个系统必须有一个最高级别的时钟,执行力最强;同时它担任着管理异步时钟的任务,其它异步时钟想让手下执行任务,必须告诉执行官,然后执行官去分配任务。所以,一切行动,都必须通过首席执行官的允许,才能进行;不然,没门。首席执行官具有最高支配权。它们之间的关系如下图所示:

因此,对于工程中出现的异步时钟,与最高时钟是对立关系,但这个CEO的地位决定了只有他说了算,不然就会“叛乱”,因此要把那些异步时钟统一管理,这就是所谓的“对立统一”。

二、异步时钟同步化

1. 异步时钟种类

异步时钟有很种类,如下是几种项目中常常出现的情况

(1)系统异步复位信号

(2)由其它处理器输入的时钟

(3)内部组合逻辑产生的时钟

当然也并非所有异步时钟都要同步化,必须高速ADC,DAC芯片往往有个时钟输入端,这时保证该芯片与该部分逻辑电路同步,可以专门供给一个晶振,来达到更好的效果;同时也不是最高时钟以外的时钟都要同步化,由PLL产生的不同的时钟,本身就是同步的,可以不处理。

当然在可靠性要求不高的时候,异步复位这些信号也可以不处理,只是,养成良好的习惯,永远不会错。

2. 异步时钟解决方案

对于时钟的同步,采用的方法都差不多。Bingo在特权的《深入浅出玩转FPGA》中得到启发,相应的简单的描述一下几种关于异步复位信号的同步化。

(1)异步复位信号的同步化

此部分其实很简单,应用了上述边沿检测的部分思维,用最高时钟打慢几拍,便实现了与最高时钟的同步。此处不再用Block来累赘的描述,verilog设计代码如下所示:

/*****************************************************

* Module Name : synchronism_design.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011-6-25

* Revision : v1.0

* Description :

*****************************************************/

module synchronism_design

(

input clk,

input rst_n,

output sys_rst_n

);

//------------------------------------------

//rst_n synchronism, is controlled by the input clk

reg rst_nr1, rst_nr2;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_nr1 <= 1'b0;

rst_nr2 <= 1'b0;

end

else

begin

rst_nr1 <= 1'b1;

rst_nr2 <= rst_nr1;

end

end

assign sys_rst_n = rst_nr2; //active low

endmodule

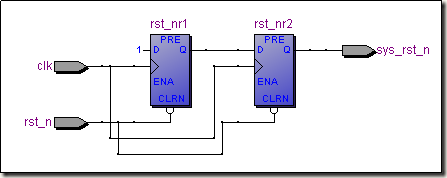

Quartus II RTL图如下:

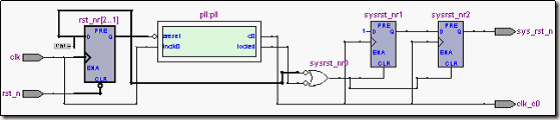

(2)PLL协作时异步复位信号同步化

相对于上述异步复位信号同步化方法的扩展,分析存在PLL环情况下的对信号的处理。如下verilog代码所示,先用晶振输入时钟对异步复位信号进行同步化,最后通过与PLL输出信号locked与前面产生的同步复位信号与操作,得到最后的系统复位信号。

具体Verilog代码如下所示:

/*****************************************************

* Module Name : synchronism_pll_design.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011-6-25

* Revision : v1.0

* Description :

*****************************************************/

module synchronism_pll_design

(

input clk, //50MHz

input rst_n, //global reset

output sys_rst_n, //system reset

output clk_c0 //50MHz

);

//----------------------------------------------

//rst_n synchronism, is controlled by the input clk

wire pll_rst;

reg rst_nr1,rst_nr2;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_nr1 <= 1'b0;

rst_nr2 <= 1'b0;

end

else

begin

rst_nr1 <= 1'b1;

rst_nr2 <= rst_nr1;

end

end

assign pll_rst = ~rst_nr2; //active High

//----------------------------------------------

//sys_rst_n synchronism, is control by the highest output clk

wire locked;

wire sysrst_nr0 = rst_nr2 & locked;

reg sysrst_nr1, sysrst_nr2;

always @(posedge clk_c0 or negedge sysrst_nr0)

begin

if(!sysrst_nr0)

begin

sysrst_nr1 <= 1'b0;

sysrst_nr2 <= 1'b0;

end

else

begin

sysrst_nr1 <= 1'b1;

sysrst_nr2 <= sysrst_nr1;

end

end

assign sys_rst_n = sysrst_nr2; //active Low

//----------------------------------------------

//Component instantiation

pll pll

(

.areset (pll_rst),

.inclk0 (clk),

.c0 (clk_c0),

.locked (locked)

);

endmodule

Quartus II RTL图如下所示:

(3)外输入异步信号同步化

当外面输入异步时钟或者异步信号的时钟,一律转换为使能时钟。此方法与前一张接关于边沿检测的讲述一样,此处不做累赘讲解。

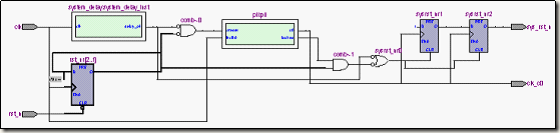

(4)系统同步信号最优化设计方案

当FPGA刚上电的短暂时间内,所有逻辑块上电,多多少少需要一定的时间(尽管非常短暂)。在一般时序要求不高的项目中,似乎可以忽略不计。但对于是需要求非常严格的操作,这几十ns或者ms上电时,FPGA内部是相当不稳定的。因此,在同步异步信号的同时,先将整个系统工作延时一定时间,将会在一定程度上得到更稳定的运行结果。同时,处理后FPGA内部真正开始工作实在系统上电稳定后进行的,因此相应逻辑时序等,更稳定准确。

以下是Bingo在实际项目中遇到的问题的解决方案。经过对系统进行100ms延时的处理后,本来容易出错的系统,在没出现过异常。

具体verilog代码如下所示:

/***************************************************

* Module Name : synchronism_pll_delay_design.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011-6-25

* Revision : v1.0

* Description :

****************************************************/

module synchronism_pll_delay_design

(

input clk, //50MHz

input rst_n, //global reset

output sys_rst_n, //system reset

output clk_c0 //50MHz

);

//----------------------------------------------

//rst_n synchronism, is controlled by the input clk

reg rst_nr1,rst_nr2;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_nr1 <= 1'b0;

rst_nr2 <= 1'b0;

end

else

begin

rst_nr1 <= 1'b1;

rst_nr2 <= rst_nr1;

end

end

//----------------------------------

//component instantiation for system_delay

wire delay_ok;

system_delay system_delay_inst

(

.clk (clk),

.delay_ok (delay_ok)

);

wire pll_rst = ~rst_nr2 & ~delay_ok; //active High

//----------------------------------------------

//Component instantiation

pll pll

(

.areset (pll_rst),

.inclk0 (clk),

.c0 (clk_c0),

.locked (locked)

);

//----------------------------------------------

//sys_rst_n synchronism, is control by the highest output clk

wire locked;

wire sysrst_nr0 = rst_nr2 & locked & delay_ok;

reg sysrst_nr1, sysrst_nr2;

always @(posedge clk_c0 or negedge sysrst_nr0)

begin

if(!sysrst_nr0)

begin

sysrst_nr1 <= 1'b0;

sysrst_nr2 <= 1'b0;

end

else

begin

sysrst_nr1 <= 1'b1;

sysrst_nr2 <= sysrst_nr1;

end

end

assign sys_rst_n = sysrst_nr2; //active Low

endmodule

//################################################//

//################################################//

module system_delay

(

input clk, //50MHz

output delay_ok

);

//------------------------------------------

// Delay 100ms for steady state

reg [22:0] cnt;

always@(posedge clk)

begin

if(cnt < 23'd50_00000) //100ms

cnt <= cnt + 1'b1;

else

cnt <= cnt;

end

//------------------------------------------

//sys_rst_n synchronism

assign delay_ok = (cnt == 23'd50_00000)? 1'b1 : 1'b0;

endmodule

Quartus II RTL图如下所示:

fpga相关文章:fpga是什么

晶振相关文章:晶振原理

评论