苹果新款处理器Q4台积电16nm制程试产

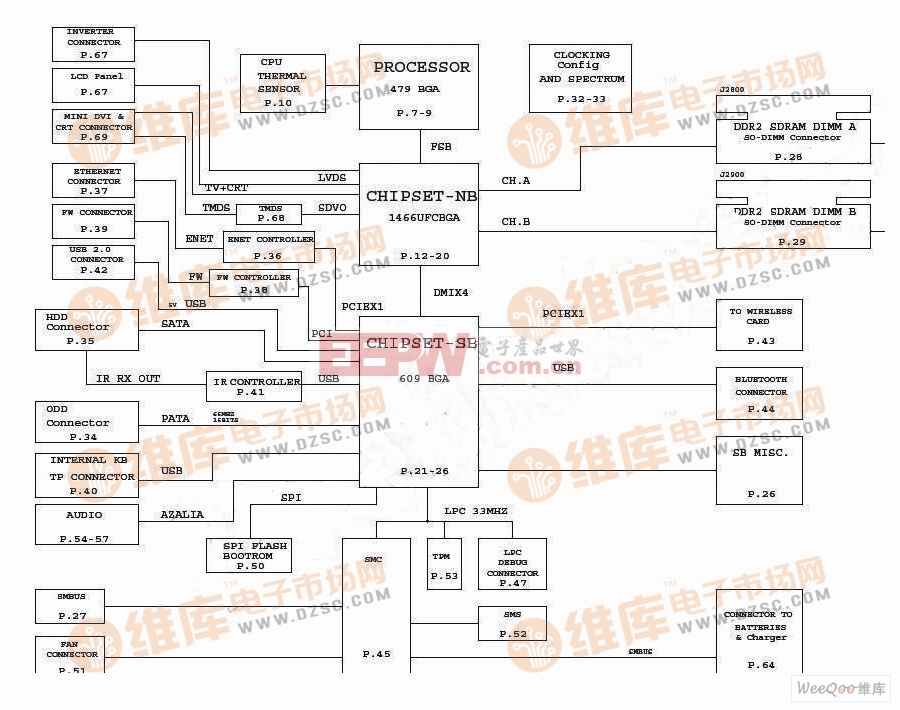

台积电16奈米先进制程布局计画

本文引用地址:https://www.eepw.com.cn/article/263459.htm晶圆代工龙头台积电(2330)全力冲刺16奈米鳍式场效电晶体(FinFET)制程,昨(25)日宣布与海思半导体(HiSilicon)合作,成功率先产出业界首颗以FinFET制程及ARM架构为基础且功能完备的网通处理器。业者分析,台积电16奈米FinFET制程投产成功,可望提前一季度时间,在今年第4季进入量产阶段。

同时根据设备业者消息,台积电16奈米FinFET Plus制程也进入试投片(try run)先前作业阶段,可望提前至第4季试产,主要客户除了绘图晶片厂辉达(NVIDIA)、可程式逻辑闸极列(FPGA)厂赛灵思(Xilinx)、手机晶片厂高通外,众所瞩目的苹果新款应用处理器也将试投片清单中。

台积电昨日宣布与海思半导体合作,成功产出业界首颗以FinFET制程及ARM架构为基础之功能完备的网通处理器,该晶片是以ARMv8架构为基础的32核心ARM Cortex-A57网通处理器,运算速度可达2.6GHz。台积电的16奈米FinFET制程能够显着改善速度与功率,并且降低漏电流,有效克服先进系统单晶片技术微缩时所产生的关键障碍。

相较于台积电的28奈米高效能行动运算(28HPM)制程,16奈米FinFET制程的晶片闸密度增加两倍,在相同功耗下速度增快逾40%,或在相同速度下功耗降低逾60%。

台积电的16奈米FinFET制程早于去年11月即完成所有可靠性验证,良率表现优异,如今进入试产阶段,为台积电与客户的产品设计定案、试产活动与初期送样打下良好基础。

藉由台积电的16奈米FinFET制程,海思得以生产具显着效能与功耗优势的全新处理器,以支援高阶网通应用产品。

评论