一种基于HD-SDI技术的高清图像处理系统设计

摘要:随着图像处理技术及传感器技术的不断发展,高清数字图像取代模拟图像成为一种趋势。设计了一种基于HD-SDI技术的高清图像处理系统,可通过FPGA+DSP架构对1080P全高清图像进行采集和字符叠加,并实时进行目标提取和偏差量计算。叠加视频可通过DVI数字接口或模拟接口实时显示。利用图像高分辨率特性,系统可实现运动目标精确跟踪。

本文引用地址:https://www.eepw.com.cn/article/263277.htm引言

随着数字视频的迅速发展,高清数字图像代替模拟图像成为必然趋势。光电系统采用全高清图像技术,不仅能大大提高显示效果,而且能显著提高系统的跟踪精度。因此,高清图像处理系统的开发成为光电系统技术发展必须突破的关键技术之一。SDI(Serial Digital Inter face)即串行数字接口,其标准由移动图像和电视工程师协会(SMPTE)制定,在当今的广播和视频产品领域得到了广泛的应用。标准规定如何通过同轴电缆在设备间传送未经压缩的串行数字视频数据。

在非编后期制作、广播电台等领域,基于HD-SDI(High Definition-Serial Digital Interface)高清电视应用较为广泛,在1.485Gb/ s、1.001 Gb/s的信号速率条件下传输的接口规格都符合标准SMPTE-292M。该接口摄像机既能保证光电系统高清显示的要求,又能满足目标实时跟踪的要求。

本文设计了一种基于HD-SDI的高清图像处理系统,可满足光电系统实现图像高清显示和目标跟踪的要求,具有较好的平台兼容性的要求。

1 系统组成

HD-SDI摄像机将高清视频通过75 Ω同轴电缆实时传送到高清图像处理系统。系统对图像进行处理后,将视频信号送到数字显示终端进行显示。

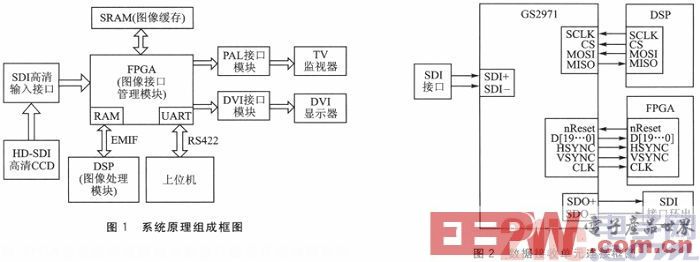

由于全高清数字图像处理系统涉及大量数据的运算及逻辑控制,系统的控制体系采用FPGA+DSP的结构形式。FPGA进行图像采集、存储、输出显示和整个系统的逻辑控制;DSP作为数字信号处理核心,则主要用来运行图像跟踪算法及完成各种外设的初始化。系统的硬件组成包括数据接收单元—HD-SDI数字视频输入;数据发送单元—HD-SDI、DVI、AV视频输出;图像存储单元—4个72 Mb SRAM;通信单元—RS422接口。系统组成框图如图1所示。

DSP选用TI公司的TMS320C26414,FPGA采用ALTERA公司的EP3C120F780,二者通过32位数据总线进行视频数据和其他参数传输。数据输入接口采用HD-SDI高清视频接口芯片对高清摄像机的视频信号进行解码,FPGA接收解码视频信号后进行图像存储和频率转换,并将图像数据传给DSP进行窗口检测、自适应图像分割、相关匹配等运算,获取目标位置相对光轴中心的偏差量。同时,FPGA通过片内双口RAM与DSP进行数据通信,完成如字符显示与消隐等功能,以方便人机界面操作。上位机通过RS422接口与FPGA进行数据通信,将测角数据、控制参数、设备状态等信息传递给图像处理系统,图像处理系统则将测偏量信息传递给上位机进行目标跟踪。

图像处理是光电系统的重要组成部分,在设计中需保持图像处理系统的通用性和开放性。采用了模块化设计思想,并采用通用通信接口代替总线与上位机通信,可保证硬件适用于不同的系统平台。各模块分别完成以下功能:

①FPGA完成图像采集、图像显示接口控制、外部存储器的读写逻辑控制及与上位机的通信。

②DSP与FPGA之间通过双口RAM实现通信,并通过FPGA读写SRAM实现目标提取和字符叠加功能。DSP实现包括目标检测、模板匹配、电子稳像等多种图像算法。

③SRAM是外扩的图像存储器,FPGA通过ping-pong方式将采集到的高清数字图像存储在SRAM中并输出给DSP和显示接口。

④数据接收单元由高速SDI接口实现高清摄像机输入视频解码。

⑤数据发送单元实现DVI、AV与SDI输出视频的编码功能。

2 数据接收单元

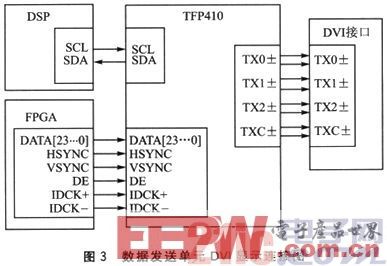

数据接收单元由SDI解码器组成。系统选用Gennum公司生产的GS2971对HD-SDI摄像机传输的视频信号进行解码,之后将高清视频信号的像素时钟、行、场及视频数据传给FPGA。数据接收单元连接框图如图2所示。

GS2971是一款自带线缆均衡功能的单端口输入解码芯片。支持3Gb/s、HD、SD SDI串行数据传输速度,最高支持4:2:2 10位色深表现,分辨率可达1080P。内置HD-SDI解串器简化了外部FPGA的逻辑解串功能。GS2971的初始化采用I/O电平控制与SPI接口相结合的方法,可被配置为20位数据输出和10位数据输出。当配置为20位数据输出时,亮度信息和色度信息分别占10位数据线,时钟为74.25 MHz;配置为10位数据输出时,亮度和色度信息合成输出,时钟为148.5 MHz。本系统中,将GS2971配置为20位数据输出模式,GS2971支持一路SDI信号环路输出,可供系统实时检测SDI信号输入是否正常。

3 数据发送单元

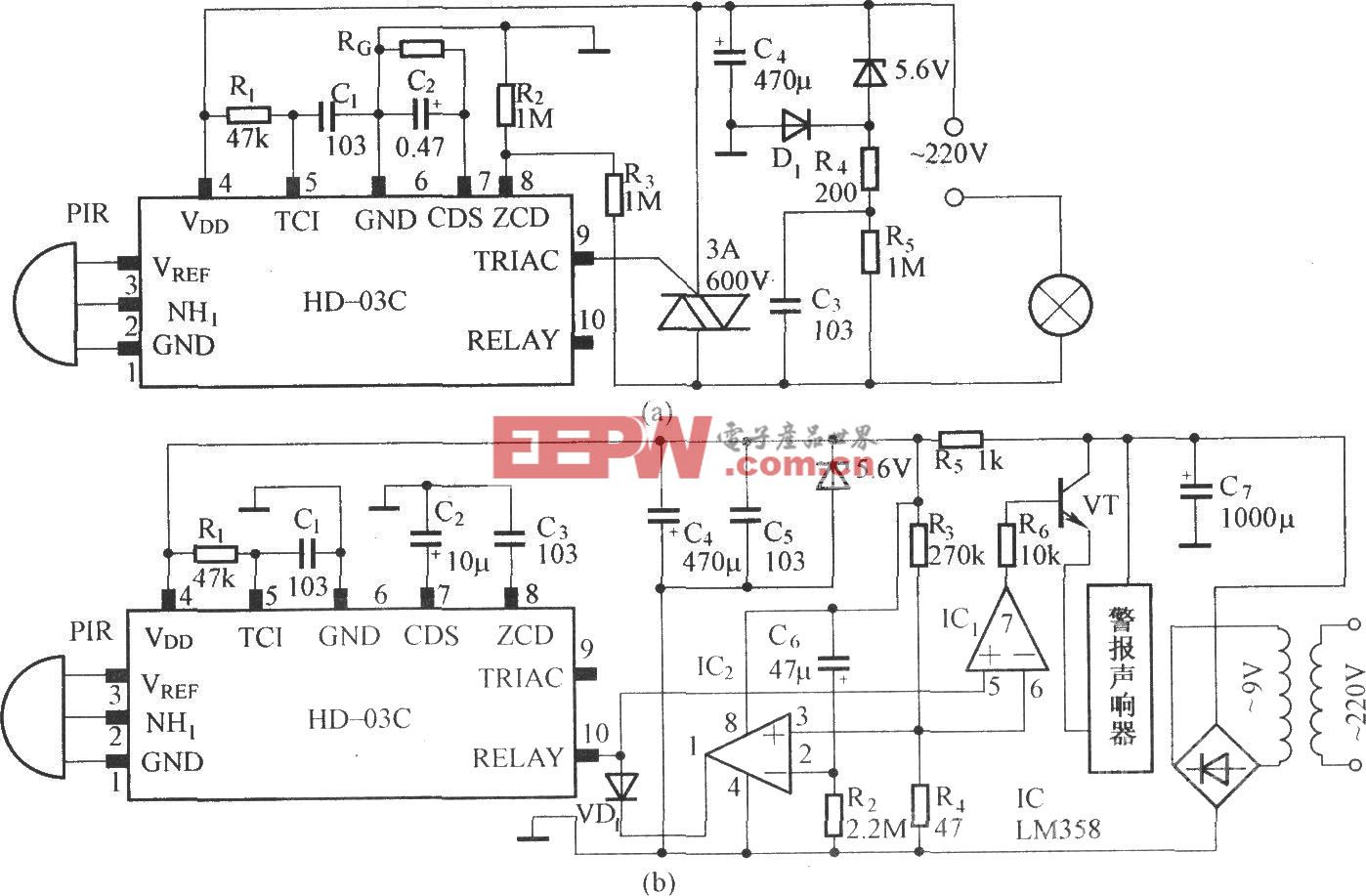

系统设计的数据发送单元由一个DVI编码器和一个PAL编码器组成。其中,DVI编码器将数字信号转换为差分信号,传递给DVI接口高清显示器。DVI接口需实现1080P高清显示,是系统数据发送单元的关键环节。

针对图像输出接口的不同要求,选择NXP公司的SAF7129实现图像的PAL制式输出;选择TI公司的TFP410实现DVI图像输出。其中,DVI显示为数字信号输出,与传统的VGA模拟信号相比,采用DVI数字信号不会引起像素抖动和相邻像素间的干扰,显示器不会造成几何失真,大大提高了画面质量,显示画面细膩、清晰,因此设计时将DVI接口作为系统的主显示通道。PAL制式为模拟信号输出,可以兼容光电系统在特殊情况下的显示需求。数据发送单元DVI显示连接如图3所示。

TFP410支持从VGA到UXGA(25~165 MHz)格式的像素速率,具有12位双边和24位单边两种输入模式,可以通过I2C总线进行芯片工作模式配置。TFP410主要通过DE引脚的高低电子来决定发送信号类型。当DE为高电平时,发送像素编码数据;当DE为低电平时,发送同步信号以及控制信号。

本设计通过I2C总线来配置编码器,编码器采用24位单边输入模式,单边输入时钟,下降沿触发。采用I2C总线可以快捷地在线调整参数配置,对编码器高速输入信号的时钟沿进行调整,有效减少图像噪声和串扰。

fpga相关文章:fpga是什么

cdma相关文章:cdma原理

评论