CMOS PA陷入成本和性能两难,“单芯片手机”梦受阻

作者:刘辉 liuh@szsia.com 本文原刊载于《集成电路应用》杂志5月刊

本文引用地址:https://www.eepw.com.cn/article/261008.htm[引言]

砷化镓PA是CMOS工艺通向“单芯片手机”之路上的最后堡垒。这个堡垒并不易攻克,因为CMOS PA的性能比不上砷化镓PA,而提高性能带来的成本增加则会让CMOS PA失去成本优势。

在基带、电源管理和射频收发等关键器件相继被CMOS工艺集成后,采用砷化镓工艺的功率放大器(PA),成为CMOS工艺通向真正的“单芯片手机”的最后堡垒。多家初创公司一直致力用CMOS PA替代砷化镓PA,其中AXIOM已经在2G手机上实现了千万级的出货量,而Javelin也宣称今年6月份将量产CMOS工艺的3G PA。

但和初创公司的高调相比,RFMD、Anadigics和英飞凌等现有供应商仍对CMOS PA持怀疑态度,认为CMOS PA很难在成本和性能上取得平衡,即使是收购了AXIOM的Skyworks也认为CMOS PA在3G和4G等高端应用市场空间有限。而SiGe半导体等公司则在走中间路线,认为取代砷化镓功放的将是SiGe BiCOMS工艺,而不是CMOS工艺。

成本和性能难以平衡,CMOS PA限于2G市场

众所周知,因为符合摩尔定律,CMOS工艺的优势是低成本、低功耗和高集成度等,从某种意义上来说,半导体技术发展的历史就是CMOS工艺进步的历史。Javelin公司的CEO Brad Fluke表示:“历史证明,一旦可以基本满足某项应用所需的性能,那么在和其它工艺的竞争中,CMOS工艺总是胜利者。”

问题是,目前CMOS PA仍然难以在成本和性能间取得平衡,CMOS PA既达不到砷化镓功放的性能,成本优势也并非绝对。

一方面,虽然CMOS晶圆比砷化镓晶圆便宜很多,但CMOS功放的面积比砷化镓功放大,最终单个器件的成本优势并不像想象的那么明显。目前6英寸GaAs晶圆可以产出大约为5,000~10,000片功放,而8英寸硅晶圆可以产出的功放数量要比这个数目少的多。这是由于CMOS器件本身的特性决定的。RFMD公司的专家表示:“在CMOS 器件中,电流是沿着晶片表面横向流动的水平电流,而砷化镓HBT工艺器件,电流流动是纵向流动的垂直电流。所以砷化镓功放可以做到比CMOS功放小50%到70%。”

另一方面,从功放应用看,相对于CMOS器件,砷化镓器件有物理材料上的优势。虽然CMOS器件这方面的缺陷可以用更复杂的设计来弥补,但是这样一来,会大幅提高成本。比如绝缘硅(SOI)技术在射频领域中的应用。相比体硅基板上的CMOS晶体管,SOI技术提升了电子迁移率,有助于缓解大功率、高效率CMOS 功放制造中的一些问题。但CMOS SOI晶圆的成本远远高于常见模拟/混合信号CMOS工艺技术的成本。因此在3G/4G应用中,CMOS的成本优势会更小,因为更高性能要求采用更复杂、昂贵的架构设计。

对此,深圳广迪克科技有限公司总经理徐杰表示:“如果采用同样的工艺节点,CMOS PA能应用的频率比砷化镓PA要低得多。”作为新兴的射频PA供应商,广迪克的砷化镓PA已经开始大量出货,据称在效率、最高功率等方面都达到了国际同类产品的水平。为了把握PA的技术发展趋势,2009年末徐杰专程前往美国考察CMOS PA技术发展情况,得出的结论是近期CMOS PA不会成为主流,因此更坚定了开发砷化镓PA的决心。

因此,在2G手机等低端应用中,由于对线性度、频率、击穿电压、峰值电流、效率的要求相对较低,不需要CMOS PA采用太过复杂、昂贵的设计,因为成本优势,未来CMOS PA的市场份额可能持续扩大,但在3G/4G等高端应用中,受限于性能和复杂设计的成本提升,CMOS PA近期不会大规模取代砷化镓功放。

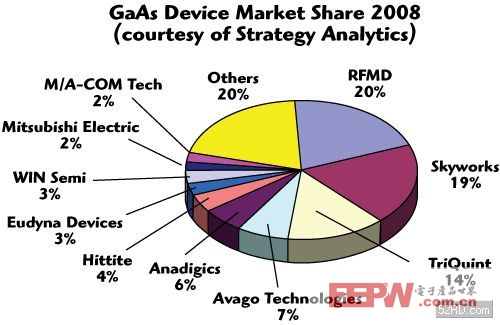

图:2008年全球砷化镓PA供应商排名

这从Skyworks已经售出总量超过 2,500 万颗的GPRS应用 CMOS功放中就可见一斑。Skyworks的市场总监Thomas表示:“在对性能不十分苛求的市场领域,CMOS PA的合理成本已经使其在 GPRS 应用上极具竞争力,成为 GaAs功放的替代产品,我们相信,这种趋势还将持续下去。”

但Thomas也坦承,在3G/4G应用上,砷化镓依然具有显著的性能优势,CMOS的成本优势也不再明显,因此在这些无线技术领域,CMOS PA的市场占有率不会有大幅提升。

例如在WCDMA应用中,大电流持续时间较长,电流达到400-500mA,而目前2G应用中的CMOS功放,电流超过300mA就无法承受。当然可以通过更复杂的架构设计提高CMOS功放的性能,但复杂的设计意味着更高的价格。

这些性能挑战是由CMOS晶体管本身的物理结构所决定的。对于CMOS功放,要提高效率,需要较小的晶体管;而要增大功率,又需要较大的晶体管,这是一个难以调和的矛盾。SiGe公司亚太区市场总监高国洪表示:“CMOS功放由于输出阻抗极低,又很难建立50欧姆负载的带宽匹配,因此 CMOS 功放输出级的“稳健性”(耐受天线阻抗大幅改变的能力)不太好。为了增强互联网接入能力,增加使用iPhone等智能电话时的多媒体性能,手机网络不断提高工作频率和带宽,CMOS 功放因此面临着越来越严峻的挑战。”

CMOS带来的“单芯片手机”梦想和现实

随着CMOS PA开始商用,将PA和同样采用CMOS工艺的基带、RF和电源管理芯片集成在一起形成真正意义上的“单芯片手机”,是业界很自然的想法,也是PA CMOS化的革命性意义所在。然而,现实是,,由于对功放和基带芯片的性能要求不同,采用的工艺节点不同,目前来看,将它们集成在一起的可能性不大。

设计功放,器件击穿电压是一个非常重要的指标。RFMD的专家表示:“对于功放,需要高击穿电压,这需要CMOS有长栅极。但是对于小信号或者基带芯片,栅极长度越来越小。CMOS功放和小信号以及基带芯片要求的硅技术是不一样的,集成在一起很困难。”

现有CMOS功放的技术节点在90nm或130nm,这就给集成CMOS功放设定了一个硬性限制,当射频收发器、基带芯片或芯片组向65nm或32nm演进时,将不得不重建功放架构。此外,正常情况下,若器件向更小的集合尺寸发展,成本会随之降低,而计算速度会进一步提升。但如果集成时要迁就90nm工艺的CMOS功放,基带芯片等的成本降低和计算速度提升就会受到限制。高国洪也表示:“把CMOS 功放与RF收发器和数字基带功能一起集成在相同的芯片上,这样做的价值实际上非常小。”Thomas甚至表示:“从芯片成品率的角度考虑,将不同工艺节点的组件集成会带来更多的成本。”

SiCMOS工艺:通往硅PA的现实路线?

硅基功放包括BiCMOS 和 CMOS器件,使用SiGe BiCMOS工艺的功放既具备接近砷化镓功放的性能,又具备低端CMOS 功放所具备的成本优势。高国洪宣称:“在短期内,取代砷化镓功放的硅基技术将是SiGe BiCMOS,而不是 CMOS。”

成本上,高国洪宣称:“尽管比起 150mm GaAs HBT晶圆,带有8至10个金属层的200mm CMOS 晶圆具有着显着的芯片成本优势,但基于现有架构的CMOS PA相对BiCMOS却没有成本优势。”高国洪解释说,这是因为现在的CMOS PA 架构是围绕RF电感的使用而构建的,能够处理大射频电流,但也因此而需要8至10个金属层。相比180nm工艺技术节点下的传统模拟/混合信号CMOS工艺技术,这些金属层的增加致使晶圆成本提高了60%以上。此外,这些电感也使芯片尺寸大为增加。考虑到额外金属层和芯片尺寸增加的影响, BiCMOS PA 和 CMOS PA的芯片级成本实际上差不多。

性能上,高国洪表示:“目前已达到量产状态 (几乎全用于手机) 的最好的CMOS功放的性能都明显不如砷化镓或BiCMOS功放。而且随着 CMOS 器件的几何尺寸缩小,要获得GaAs 或 BiCMOS 功放性能变得更困难, 要生产出能够克服这种缺点的CMOS 功放还得进行更多的研究工作,并需要新的架构。CMOS PA架构若没有重大的突破和创新,不可能克服其性能缺陷。”虽然SOI技术具有提升CMOS PA性能的潜力,但SOI的成本居高不下。高国洪认为,用于射频功放的CMOS SOI还需要数年时间才能够将成本降至BiCMOS的芯片级成本水平。

在WLAN应用中BiCMOS功放已逐渐开始取代砷化镓功放,而LTE、WiMAX和WLAN应用相似,它们都使用了正交频分复用(OFDM)技术。高国洪表示:“在4G手机和移动设备中,鉴于硅锗BiCMOS 是一种广泛可用的制造工艺,而目前又在WLAN领域拥有强大的主导地位,所以在手机功放和前端模块产品领域中,硅技术最终将取代GaAs似乎已是大势所趋。”当然他强调,手机中GaAs PA最合逻辑的取代方法是转向硅基技术,而非特定硅CMOS。因为以硅锗BiCMOS为首的硅BiCMOS,具有CMOS的所有成本优势和作为GaAs工艺核心的异质结双极型晶体管(HBT)的性能优点。

评论