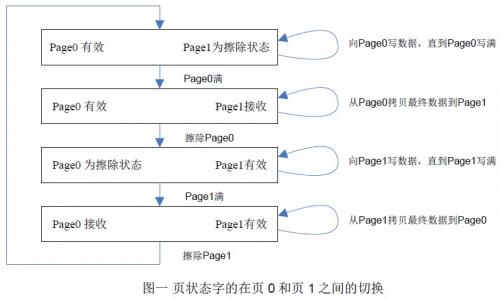

轻松实现负电压跟踪

我们向任何同步降压转换器添加一个简单的电路,就能生成跟踪负输出,该跟踪负输出可实现较好的稳压作用,并降低成本,减少占用面积,同时提高效率。

本文引用地址:https://www.eepw.com.cn/article/258755.htm高速服务器、工作站和时钟分配网络等应用都需要晶体管-晶体管逻辑 (TTL) 和发射极耦合逻辑 (ECL) 转换器。差动 ECL 器件通常需要正负输出电压。输入电源为正直流电压时,我们可用几种方法来实现电压逆变,从而获得所需的负输出电压。

我们可采用的拓扑包括充电泵、反相降压/升压转换器以及 Cuk 转换器等。每种方法都需要专门的控制电路进行调节。除了充电泵之外,每个功率级还需要电感器、FET 和二极管等多个组件。反相充电泵占用面积较小,但在负载升高时,不但效率不高,而且稳压效果也不是很理想。

反向和其他变压器设计方法也是我们的可选方案。只有在需要系统实现其他高功率输出电压的情况下,我们才选择这些方法。在这种情况下,负 5V 输出电压应通过变压器辅助绕组的线性稳压器进行二次稳压 (post-regulated)。但上述方法都不能同时实现低成本、高性能和减小占用面积的优势。下面我们介绍一款简单的解决方案,可以解决上述所有问题。

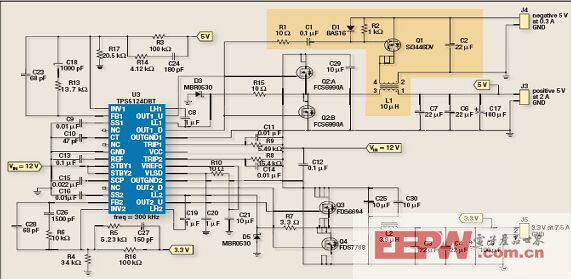

图 1 所示的双同步降压转换器为正 5V 输出电压和系统定义的另一款输出电压(本例中为 3.3 V)的典型设计解决方案。突出显示框中的电路显示了生成负 5V 输出电压所用的额外组件。正 5V 电路作为标准的同步降压转换器工作,其开关循环包括两个组成部分。

|

| 图1、为该双同步降压转换器在添加最少量的组件(见突出显示框)就可提供负输出电压。 |

在开关循环的第一阶段,顶部 FET Q2A 开始进行传导,并在电感器 L1 的引脚 3-1 上施加一个电压 (VIN – VOUT)。这时 FET Q2B 和 Q1 将关闭,而负 5V 输出电容 C2 则提供全部的负 5V 输出电流。C2 的大小必须适当,这样才能在本阶段提供负 5V 电流,并保证负 5V 输出纹波电压在限定范围以内。

Q1 关闭时,必须阻挡相当于负 5V 输出电压加上 L1 辅助绕组上耦合电压大小的电压。在 L1 匝比为 1:1 的情况下,Q1 的阻塞电压基本等于输入电压。

差动放射极耦合逻辑器件通常同时需要正负输出电压

在开关循环的第二阶段,控制器将顶部 FET Q2A 关闭,并将底部 FET Q2B 和 Q1 开启。电感器 L1 引脚 1-3 上的电压必须得到逆变,以保持电流流向相同(进入输出端),这就会在耦合电感器绕组“单点”上产生正电压。L1 引脚 1-3 上的电压振幅固定于一定的水平,即相当于输出电压与 Q2B 相对较低的压降之和。

请注意,在底部 FET Q2B 传导过程中,电流以顺时针方向流经电感器和负载,并流经底部 FET Q2B 和电感器返回。在此传导阶段,耦合电感器次级绕组引脚 2-4 的电压等于引脚 1-3 上的电压,因为两个绕组的匝数相同。由于 FET Q1 开启,因此电流从次级绕组流向负载,同时也会给 C2 充电。

负输出的电压等于电感器的次级电压减去 FET Q1 的传导压降以及电感器的电阻性压降。我们应选择低绕组电阻的电感器以及低导通电阻的 FET,这样就能将压降最小化,从而减少负 5V 输出随负载增加而出现的差异。最小化底部 FET Q2B 的导通电阻还有助于改进负 5V 输出的稳压作用,因为该压降与正 5V 输出电流成正比。

我们可以注意到这样一种有趣的情况,即 FET Q2B 的压降越大,负 5V 输出的负极性就越强。在一定的正 5V 和负 5V 输出负载条件下,FET Q2B 和 Q1 的压降可能会相互抵消,从而实现完美的输出电压匹配。

Q1 的栅极驱动电压来自底部 FET Q2B 的栅极驱动电压,因为两个 FET 都同相地 (in-phase) 协调工作。底部 FET 栅-源电压的峰至峰振幅根据控制器设置为 5V。电容 C1 交流耦合于该开关信号,但阻塞直流平均电平。二极管 D1 仅在负电压摆动时进行传导,将 Q1 的栅极电压固定于源引脚 0.7V 以下,并将其关闭。

在正电压摆动时,峰值电压会比关闭时大 5V,这就形成了约为 4.3V 的正栅-源电压,并开启 Q1。我们必须使用栅-源阈值电压为 2.5V 的 MOSFET,这样才能确保 Q1 全面增强。使用二极管 D1 后,可以确保几乎所有可用的驱动电压振幅(不到一个二极管压降)都能用作正向栅-源电压。

如果没有 D1,那么正向栅-源电压振幅就会随着占空比变化而变化。输入电压最高时,其振幅最低,这就会增加 Q1 不能正常开启的几率。主体二极管 Q1 在 FET 开关交换时间(在 Q1 完全开启前)内允许负 5V 电流通过其传导,但不能提供良好输出稳压所需的较低正向压降。我们针对 Q1 采用了 N 通道器件,从而实现了比 p 通道器件更低的 RDS(ON) 值,而且还将目前市场上可用的商用器件的选择范围拓宽了许多。

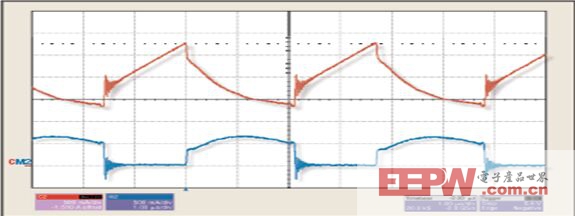

图 2 显示了 FET Q1 以接地和负 5V 输出电压为参考测量所得的栅极电压。电阻 R1 和 Q1 输入电容提供了波形边缘的高频过滤功能,而电阻 R2 则提供了低阻抗下拉功能,以避免驱动信号浮动。

|

| 图2、图1中的电路测量结果显示了Q1栅极电压波形(顶部跟踪)和负5V输出电压波形(底部跟踪)。(振幅比例为2V/div 而时间比例为1μs/div。) |

图 3 显示了满负载情况下,在电感器 L1 一级和次级绕组上测量得出的电流。我们可以看到,正 5V 电感器电流(顶部)中,电流的下坡部分必须同时为正 5V 和负 5V 输出提供电流,而且还要为负 5V 输出电容充电,这就使一级峰至峰纹波电流提高了近 50%,因此必须在正 5V 输出上采用更多输出电容,这样才能保持输出纹波电压较低。

|

| 图3、图1所示电路中,显示了满负载情况下在电感器L1一级绕组(顶部跟踪,引脚3)和次级绕组(底部跟踪,引脚4)上测量得出的电流。(振幅比例为500 mA/div而时间比例为1 μs/div。) |

由于次级绕组电流为脉冲形式,因此会对负 5V 输出电容形成较大负担。不难看出,负 5V 负载电流较大时,正 5V 和负 5V 输出需要很大的输出电容才能保持合理的纹波电压。因此,我们建议负输出上的负载相对于正输出而言要低一些。

本例中的电路采用 Coiltronics DRQ127 耦合电感器,其绕组电阻很低,但直流电流的额定值却较高。其采用标准尺寸封装,仅比功能相当的单绕组电感器略大一些,成本的增加也非常有限。我们只有在尽可能降低绕组电阻的情况下才能实现最佳的电路性能,因为绕组电阻随着负载增加会影响稳压性能。

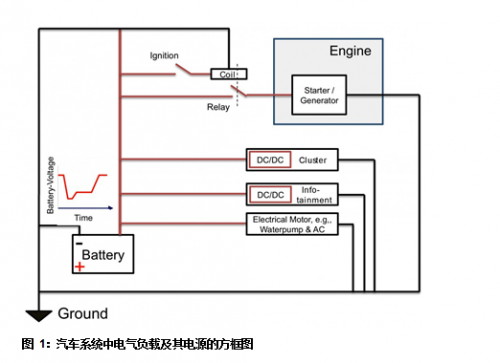

图4显示了加电时的输出电压波形。负 5V 能准确跟踪正 5V,因为电感器的次级绕组电压以逐脉冲的方式固定在正 5V 输出电压。无论正 5V 输出电压情况如何,负电压都可以根据 Q2B 上较小的压降以及 Q1 和 L1 的绕组电阻进行准确地跟踪。

|

| 图4、图1中的正5-V(顶部跟踪)和负5-V(底部跟踪)输出电压在起动时紧密跟踪。(振幅比例为2 V/div而时间比例为2 ms/div。) |

在图 5 中负 5-V 输出的测量显示了其负载稳压功能。该曲线显示了负 5V 电压加载时的差异,每个曲线都为不同的正 5V 负载。不同负载情况下,电压稳压差异在 ±1% 以内,正 5V 输出交叉负载也会有 ±1% 的差异,从而使整体输出差异为 ±2%。附加电路所引起的损耗非常低,在大多数加载情况下,输出效率可达 95%。

|

| 图5、图1中电路的负5-V输出提供良好的交叉稳压性能。 |

作者:德州仪器 (TI) 应用工程师 John Betten

评论