利用DSP与FPGA的光栅地震检波器的信号处理

0 引 言

在石油地震勘探中,地震仪通过地震检波器采集信号。地震检波器是为了接收和记录地震波而设计的一种精密的机械、电子组合装置,是地震勘探数据采集中的重要环节,其性能好坏直接影响地震记录质量和地震资料的解释工作。光栅传感技术的发展为检波器的设计提供了有力的手段。其光栅信号处理技术仍局限于低速度的信号处理,虽然测量精度较高,但其动态特性难以满足振动信号检测等高速变化信号的处理要求,本文设计了一种利用DSP与FPGA结合的光栅振动信号处理系统,它主要完成对光栅震动传感器输出的两路正交的正弦波信号的采集、计数、高倍细分等,从而实现了对快速的振动信号的复现。

1 光栅地震检波器的工作原理

光栅地震检波器主要由光源(白光或单色光)、准直镜、光电池、指示光栅(副光栅)、光栅谐振子(主光栅)组成。光栅谐振子(主光栅)为检波器的可动部分,由上弹簧片和下弹簧片支撑。工作时,检波器外壳通过检波器尾钉与大地连接并固定,当大地受到震源激发后,地震波传至地面引起地面震动,检波器外壳也随之震动。而光栅振子由于弹簧片的弹性和本身的惯性,有保持绝对不动的趋势,从而产生了光栅振子与外壳的相对运动,也就是说光栅副中的主光栅与裂向式指示光栅之间产生了相对运动。两块叠放在一起的光栅具有了相对运动也就会产生与之相对应的莫尔条纹,从而在相位差为90°的四个光电池上产生莫尔条纹的变化,于是光信号被转化为电信号,再经差分放大后形成两路相位相差90°的正弦或余弦波信号。

2 光栅震动信号的同步采集

要保证整个系统对振动信号的实时复现,关键是要保证对两路模拟正弦波的同步采集。若使用DSP直接控制多通道的模数转换器,由于编程语言的顺序结构和单个模数转换器不能同时采样保持的限制,对于多路信号的采集只能分时多通道顺序采集,这样对同一点的两路模拟波的采集肯定会产生相位差,这样对复现出来的原振动信号会造成相当大的失真。但是由于FPGA的编程语言VHDL执行时是并发执行的,并不受到它们在主结构中的编写顺序的影响。根据上述特点,对于本系统的设计可以分成三个并行进程,分别是2个光栅信号采集的进程和一个加减计数器的进程。

AD转换器选用的是LINEAR公司生产的LTC1606,该器件是具有采样保持功能的16位250kHzADC。该ADC分辨率高,采样速率高、功耗小,可在高精度的数据采集系统中广泛应用。

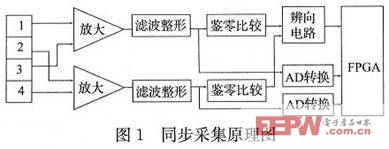

光栅振动莫尔条纹的信号采集采用成直线排列的相位差为90°的四个光电池,分别记为1、2、3和4,如图1所示。它们接收由被测振动信号调制的莫尔条纹,并通过差动放大器、整形滤波器输出两路正交的正弦信号。这两路信号分成两组,其中一组经过鉴零比较电路转换成方波送入辨向电路为FPGA中加减计数器提供计数累加值和辨向信号。另一组则直接将放大的模拟电压信号送入两路AD转换器转换成数字量并存入FPGA。在FPGA中开辟3个双口RAM存储器用来顺序存放每一点的整周期计数值和两路波形的数字量,为DSP进行高倍细分提供基础数据。

2.1 双口RAM的设计

双口RAM是常见的共享式多端口存储器,双口RAM最大的特点是存储数据共享。一个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。由于硬件双口RAM接口时序复杂,成本高也会给系统带来不稳定性,因此本文在FPGA中设计了一软RAM,用来缓冲数据采集与处理之间产生的异步时差。

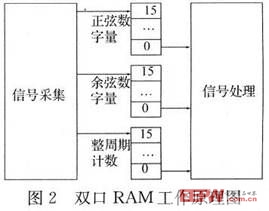

其工作原理如图2所示,所设计的存储空间为3个16字容量的双口RAM,当信号采集部分向新地址写入每一个振动点的三个信息量时(图中所示地址为15),信号处理部分则读取先前振动点的三个信息量进行细分等处理(图中所示地址为0),当双口RAM写满数据后,写地址指针又会重新定位到首地址写入新的数据,这种缓存结构的设立不会丢失信息点,保证了还原信号的连续性和可靠性,虽然还原信号滞后源信号3到4个字的时间,但保证了每一个点三个信息量的同步性,这是C语言等顺序结构语言所无法达到的。

2.2 双口RAM的流程图设计

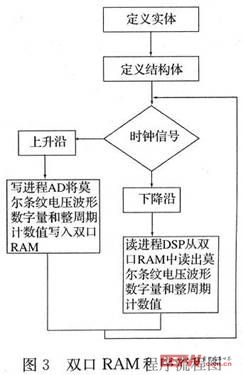

首先是定义实体与外部端口,包括时钟、输入输出、读写地址端口。它们的作用分别是:

1)时钟端口:利用时钟的脉冲边沿来触发读写进程,使得新旧数据在双口RAM中交替进出。

2)输入输出端口:分别为16位的位矢量类型,用来保证与16位AD和DSP的数据格式匹配。

3)读写地址端口:2位的位矢量类型,用来设置16位字的存储器容量,并在读写RAM操作时提供地址选址信号。

其次是定义结构体,包括定义内部缓冲地址信号,并定义了一个容量为16字的Mem(存储器类型)型变量。

最后是并发进程的定义,包括写进程和读进程的定义,以时钟的脉冲信号作为敏感信号来触发进程的启动,每一个时钟周期完成一次对RAM的读写,其中时钟频率由FPGA根据AD的采样速度和DSP的处理速度来设定,要保证当采集信号写入尾地址的时刻,至少要保证首地址已经被DSP所读取。图3为双口RAM程序流程图。

2.3 双口RAM的仿真结果

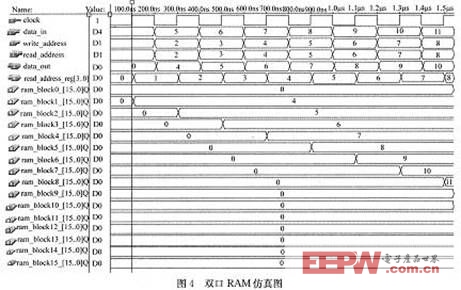

图4为该进程的仿真时序图,由图可见第一个时钟的上升沿数据输入端口data_in的值为4,这时写选通端口write_address选通地址1,然后对应着地址1的存储器模块ram_block1的内的值在此刻刷新为4,这说明写进程正确。同时应注意到读地址选通信号read_address的值被传递到读地址寄存器read_address_reg中,read_address_reg中的值被刷新为1。当第一个时钟的下降沿到来时,信号输出端口data_out根据读地址寄存器read_address_reg中的地址值1选通ram_block1,此时data_out的值刷新为4,这说明读进程也正确。

3 DSP的软件细分

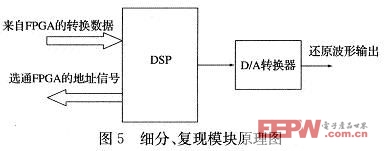

采用大数可逆计数与小数细分计数的软件细分技术。其中大数计数是对莫尔条纹整周期数进行可逆的加减计数,这部分功能有采集模块中的FPGA来完成,小数计数是对莫尔条纹不到一个周期信号细分结果进行计数,其功能由DSP来完成。运算的结果为大数计数结果乘以光栅栅距与小数计数结果乘以细分当量之和,其中细分当量为光栅栅距除以细分倍数。该模块的硬件原理图如图5所示。

通过DSP的地址选通线依次选通读取FPGA中三个数据缓存区中的数据,缓存区分别存放两路模拟信号的数字量与加减计数器的累加计数值,然后利用公式R=N*w+K*L求出任意一点谐振子的幅值并输出。式中N为整周期的累加计数值,W为光栅栅距,K为细分计数,L=W/M,M为细分倍数。该细分模块主要是完成对细分计数K值、和幅值R值的求取,并完成对幅值的数字量转换并输出。

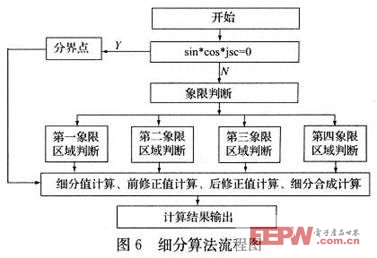

其中细分方法也就是对K值的求取采用了八卦限幅值分割法,根据上述方法设计了细分倍数可变的细分算法,利用DSP C语言的专用库函数实现了纯计算的算法。细分算法流程如图6所示。

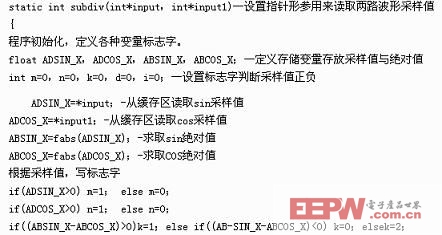

由幅值细分法可知,软件细分算法设计的关键问题是根据两路信号的比值对该点的相位角的正确定位。该点的位置有两种情况,一种是落在各象限的边界上,另一种是落在各象限之中。根据细分边界条件判断该点的采样数据是否发生在四个象限的分界线上,如果判断此次换向发生在象限的分界线上,则细分数为固定值,并且通过象限的正负关系就可以确定具体细分数值,不需要进行复杂的计算。如果该点不是发生在象限分界线上,则需根据象限正负关系判断换向发生的具体象限,不同象限对应不同计算公式。细分算法程序如下:

根据标志字判断相位点的位置,根据相应位置不同公式求取细分值

然后利用公式R=N×ω+d×L求出任意一点谐振子的幅值并输出。式中N为整周期的累加计数值,W为光栅栅距,d为细分计数,L=ω/m,m为细分倍数。

4 结束语

设计的光栅地震检波器充分结合了FPGA的强大控制功能和DSP高速运算处理功能,实现了信号的同步采集、高倍细分和实时复现。减少了单一处理器的负荷,提高了系统的速度和稳定性,为光栅震动信号处理提出了一个新思路。由于硬件双口RAM接口时序复杂,成本高也会给系统带来不稳定性,因此本文在FPGA中设计了一软RAM。对于振动信号幅值的计算则是在对整周期的莫尔条纹进行计数的同时,利用软件细分法实时地计算出非整周期的莫尔条纹信号所代表的小数值,并实时将二者相加后乘以莫尔条纹当量(每个莫尔条纹所代表的位移量),即可得到信号的实时振动幅值。

评论