基于FPGA/CPLD的VGA显示系统设计

VGA(视频图形阵列Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

本文引用地址:https://www.eepw.com.cn/article/256480.htm目前 VGA技术的应用还主要基于 VGA显示卡的,而在一些既要求显示彩色高分辨率图像又不使用计算机的设备上,VGA技术的应用却很少。本文对基于 FPGA/CPLD的嵌入式 VGA显示的实现方法进行了研究。

基于 FPGA/CPLD的嵌入式 VGA显示系统,可以在不使用 VGA显示卡的情况下实现 VGA图像的显示和控制。该系统具有成本低、结构简单、应用灵活的优点。

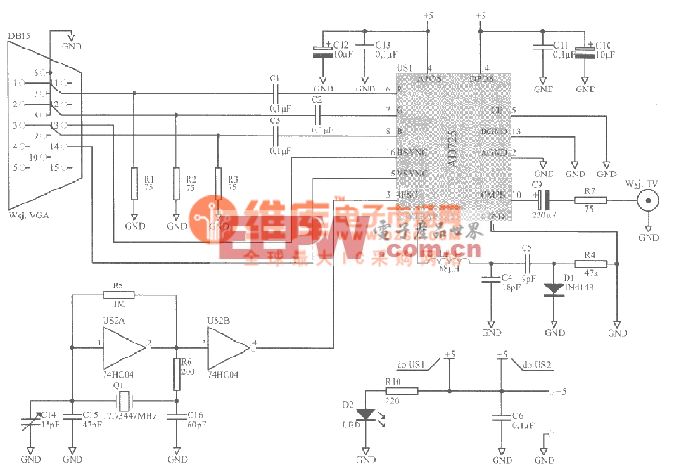

通用 VGA显示卡系统主要由控制电路、显示缓存区和视频 BIOS程序三个部分组成。其控制电路主要完成时序发生、显示缓冲区数据操作等功能;显示缓冲区提供显示数据缓存空间;视频BIOS作为控制程序固化在显示卡的 ROM中。在基于FPGA/CPLD的嵌入式VGA显示系统的设计中,可以使用很少的资源,就产生 VGA各种控制信号,达到显示彩色高分辨率图像的要求,而不需用 VGA显示卡和计算机设备。图 1是基于 FPGA/CPLD的嵌入式 VGA显示系统的结构框图,图中FPGA采用的是Altera公司Cyclone II系列的EP2C35F672C这款 FPGA.Cyclone II器件采用 90nm、低 K值电介质工艺,通过使硅片面积最小化,可以在单芯片上支持复杂的数字系统。EP2C35F672C该芯片提供了 33216个逻辑单元 ,包括了嵌入式 18*18位乘法器、专用外部存储器接口电路、 4KB嵌入式存储器件、4个锁相环和高速差分 I/O等功能。该芯片的工作频率和引脚 IO等资源都能很好的满足本系统的要求.FPGA的工作时钟为 54MHz。

VGA接口芯片采用了 ADV7125,该芯片是美国 ADI公司生产的高速视频数模转换芯片,其像素扫描时钟频率有 50MHz、140 MHz、270 MHz、330MHz四个等级。ADV7125在单芯片上整合了三组 8位高速 D/A转换器,可以分别处理红、绿、蓝视频数据,特别适用于高分辨率模拟接口的显示终端和要求高速 D/A转换的应用系统。 ADV7125的输入及控制信号非常简单:3组 8位的数字视频数据输入端,分别对应 RGB视频数据,数据输入端采用标准 TTL电平接口;4条视频控制信号线包括复合同步信号 SYNC、消隐信号 BLANK、白电平参考信号 REF WHITE和像素时钟信号 CLOCK;外接一个 1.23 V数模转换参考电压源和 1个输出满度调节。只有 4条输出信号线:模拟 RGB信号采用高阻电流源输出方式,可以直接驱动 75Ω同轴传输线。

2模块划分与模块功能定义

FPGA中包含了四个工作模块: VGA时序发生器模块、VGA图像显示调色板模块、数据存储器和数据读写控制器。由于 ADV7125内部没有颜色的转换器 ,所以当数据存储器中的数据为 YUV信号时,就要把 YUV信号转换成 RGB信号,这一功能就是由 VGA图像显示调色板模块完成的,当显示数据为 RGB信号时,数据可以直接传输到 ADV7125,不需调色板进行颜色转换。数据存储器和数据读写控制器解决了显示数据的来源和数据的存储。用 FPGA对图像进行存储和整理,并产生驱动电路需要的各种控制波形由视频控制器对颜色缓冲器进行扫描,其中视频控制器可以读取像素颜色,用这些颜色来控制输出设备的亮度。

VGA时序发生器模块产生显示器所需的时序,这是完成设计的关键,时序稍有偏差,显示必然不正常,甚至会损坏彩色显示器。

3、 VGA时序分析

显示器采用光栅扫描方式,即轰击荧光屏的电子束在 CRT(阴极射线管)屏幕上从左到右(受水平同步信号 HSYNC控制)、从上到下(受垂直同步信号 VSYNC控制)做有规律的移动。光栅扫描又分逐行扫描和隔行扫描。隔行扫描指电子束在扫描时每隔一行扫一线,完成一屏后再返回来扫描剩下的线,与电视机的原理一样。隔行扫描的显示器扫描闪烁的比较厉害,会让使用者的眼睛疲劳。目前微机所用显示器几乎都是逐行扫描。逐行扫描是指扫描从屏幕左上角一点开始,从左向右逐点进行扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;当扫描完所有行,形成一帧时,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行行场消隐,开始下一帧的扫描。

完成一行扫描所需时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描所需的时间称为垂直扫描时间,其倒数为垂直扫描频率,又称刷新频率,即刷新一屏的频率。常见的有 60Hz、75Hz等。

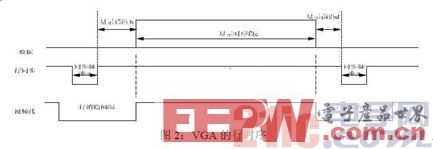

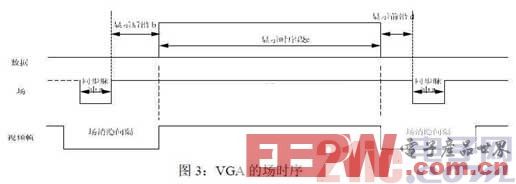

VGA 显示器要正确显示图像关键还是如何实现 VGA时序。视频电子标准协会( VESA, Video Electronics Standards Association)对显示器时序进行了规范。 VGA的标准参考显示时序如图 2、图 3所示。行时序和场时序都需要产生同步脉冲(Sync a)、显示后沿 (Back porch b)、显示时序段(Display interval c)和显示前沿 (Front porch d)四个部分。 VGA工业标准显示模式要求:行同步、场同步都为负极性,即同步头脉冲要求是负脉冲。

VGA的行时序如图 2所示:每一行都有一个负极性行同步脉冲( Sync a),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿 (Back porch b),在显示时序段(Display interval c)显示器为亮的过程,RGB数据驱动一行上的每一个象素点,从而显示一行。在一行的最后为显示后沿(Back porch b)。在显示时序段( Display interval c)之外没有图像投射到屏幕时插入消隐信号。同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)都是在行消隐间隔内( Horizontal Blanking Interval),当行消隐有效时, RGB 信号无效,屏幕不显示数据。

VGA的场时序与 VGA的行时序基本一样,如图 3所示,每一帧的负极性帧同步脉冲(Sync a)是一帧的结束标志,同时也是下一帧的开始标志。而显示数据是一帧的所有行数据。

fpga相关文章:fpga是什么

led显示器相关文章:led显示器原理

锁相环相关文章:锁相环原理

评论