基于FPGA的2M误码测试仪系统的设计方案

0 引言

无论是何种通信新业务的推出和运营,都离不开强力有效且高可靠的传输系统。随之而带来的问题就是如何对系统的传输质量进行测量和保证。

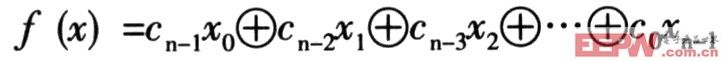

误码测试仪是一种能够测量和保证传输质量的智能化仪器,该仪器可通过检测来反映数据传输设备及其信道工作的误码损伤性能质量指标,并对其进行传输质量分析的有效工具。在电信运营、工程验收、科研、设备生产、教学实验等各方面,误码仪都是必不可少的通信测量和线路维护的最佳辅助工具。目前在陕西省业务设备的接口应用中,百分之九十以上的接口是2M的接口,比如:交换网络上应用、信令网上的应用、数据网上的应用、网管网上的应用等,都使用了2M的数据。针对传统误码仪的不足,本文给出了基于Altera公司的cyclone系列FPGA芯片EP1C12-240PQFP的2M误码测试仪的设计方案。基于FP- GA的误码测试仪相对于传统的误码测试仪的优点在于其FPGA的内部逻辑功能是通过向内部静态存储器单元加载配置数据来实现的。其配置文件决定了逻辑单元的逻辑功能以及模块间或与I/O间的连接,并最终决定了FPGA所实现的功能。FPGA的这种结构允许多次编程,并享有快速有效地对新设计进行优化的灵活性,故现今的通信系统大量采用FPGA作为系统的核心控制器件。本文重点介绍了FPGA内核中序列发生模块和序列接收模块中核心内容的设计。其中FPGA 内核中m序列发生器的设计思想采用移位寄存器理论,并根据本原多项式来获得m序列移位寄存器的反馈逻辑式:

其中cn-1-i∈GF(2)是反馈系数,xi∈GF(2)是每位寄存器的状态。这样,结合cyclone系列FPGA芯片EP1C12-240PQFP的结构特点,就很容易实现反馈移位寄存器的逻辑功能。

1 误码测试系统的总体方案

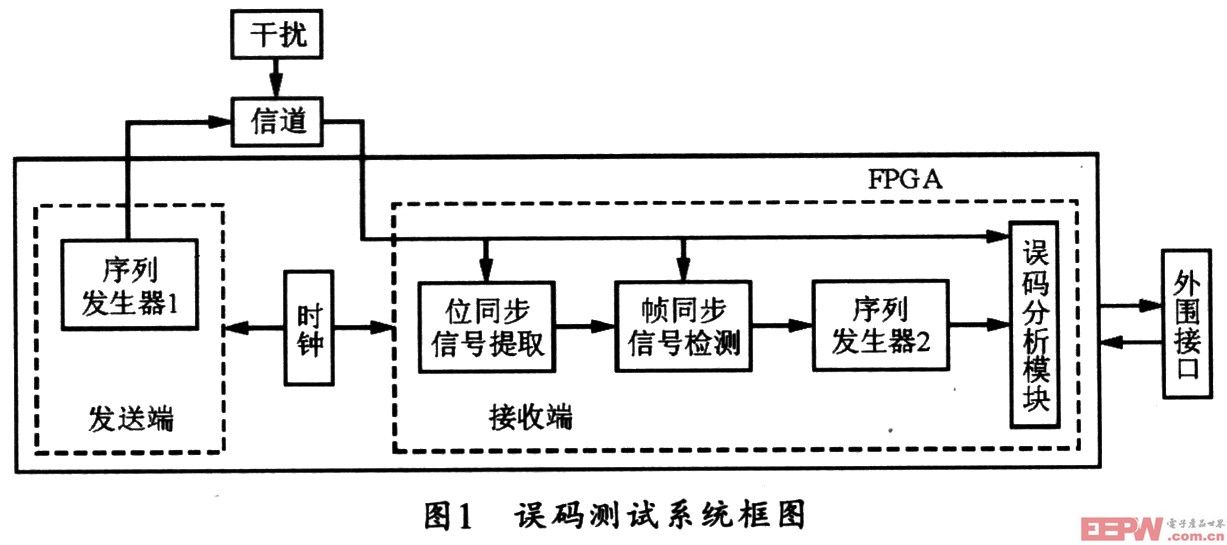

误码一般是由通信系统中接收端抽样判决器的错误判断造成的,而造成错误判断的原因主要有两个:一是码间串扰,另一个是信道加性噪声的影响。误码测试仪存在两种设计方案,一种是误码仪的发射端模块和接收模块两部分独立,可用于单工的通信系统性能测试。但是由于该系统的测试序列需要动态生成,所以,其能够测试的系统码速只能和FPGA控制模块所能达到的速度相同。另一种方案是将发射端模块和接收模块结合在一个系统内部,这样能测试具有回环的通信系统,如双工通信的收发设备等。本文设计属于第二种方案,其误码测试系统框图如图1所示。图中,发送端模块产生的伪随机序列作为通信系统的信源数据流流经信道,接收端模块则接收来自信道输出的比特流,并将其与接收端模块产生的与发送端模块输出类型相同的伪随机序列进行比较,从而完成误码测试。误码仪由发送端的序列发生器 1模快、接收端的位同步信号提取模块、帧同步码检测模块、序列发生器2模块、误码分析模块及外设接口构成。其中位同步信号提取模块的作用是获得位定时同步脉冲。帧同步码检测模块的作用是获取帧同步信号,以使两个序列能以同相位比较计算误码率。因为如果接收的测试序列与序列发生器2模块产生的序列两者相位不同,则误码的测试结果将毫无意义。

2 系统硬件设计

2.1 系统硬件组成

根据误码测试仪器的功能要求,在本系统的硬件总体架构中,将FPGA作为总控制器,并外扩E1接口模块,以用于实现码型和波形的转换,同时将FPGA输出的NRZ码型转换成适合于在E1信道中传输的HDB3码型,并将来自E1信道的HDB3码转换为NRZ码送入FPGA中;E2PROM存储模块则可将误码分析模块的误码测试结果进行存储,且掉电不丢失数据,并可随时读取,以便于在无人值守的情况下进行误码测试;LCM显示模块是为了使用户了解误码测试结果;RS232串口模块则用于和PC机通讯,上传误码检测结果,以便于从PC机上看到一段时间内误码率曲线图及其它误码信息,使用户了解通信系统的误码发生情况;此外,系统还外扩有键盘、

评论