基于FPGA的高清低码流H.264摄像机设计

摘要:本文提出了一种基于低成本FPGA的高清低码流安防摄像机SoC实现方式,该设计已经完全实现,开创了高清低码流安防摄像机SoC的先河。

本文引用地址:https://www.eepw.com.cn/article/247781.htm1. 概述

目前高清H.264摄像机的核心SoC基本上都是ASIC,而FPGA作为近年来发展迅速的可编程器件,在高清H.264摄像机的SoC领域如何能有一席之地?这是我们的设计需要实现的目标。

2. 设计特点

与ASIC相比,FPGA的特点是功能强,设计灵活,随时升级,工作成果可以积累,NRE低,但是芯片价格比ASIC贵,所以必须找到一个可以达到价格平衡的应用领域,我们根据这几年智能手机和3G网络发展迅猛的情况,参考电信运营商第一代全球眼的技术指标,直接把设计指标定位在码流小于512kbps和分辨率为1280x720x25fps,目前在市面上可以实现这些指标的摄像机几乎没有,这是FPGA的好机会。

512kbps的码流限制主要是考虑到ADSL和家庭光端机的上传能力,而且也能利用3G上传视频,减少了智能手机的码流下载压力;1280x720是智能手机的主流分辨率,自然需要相应的视频源,如果显示D1或CIF,效果肯定不理想。

我 们的目标是做一个可以直接用于生产的参考设计,除了设计指标先进,我们还要考虑价格和实用,所以我们选择了低成本的CYCLONE IV系列,另外也实现了一般网络摄像机的全部功能,如H.264压缩、720p25帧三码流、双向语音、重要区域和隐私区域的定义、智能分析、移动检测、 声音侦测、POE供电等;

3. 实现高清低码流H.264摄像机SoC的关键

一般来说,1280×720×25fps的码流在2Mbps左右,如何降低码流?除了使用mail profile with cabac的H.264编码器外,还需要对视频图像进行分析,而且要在帧率、分辨率、视频质量等方面权衡折中,在512kbps码流下获得最好的视频效果,为了达到这样的目的,需要复杂灵活的控制,FPGA可以满足这样的需求。

4. 高清低码流H.264摄像机的结构

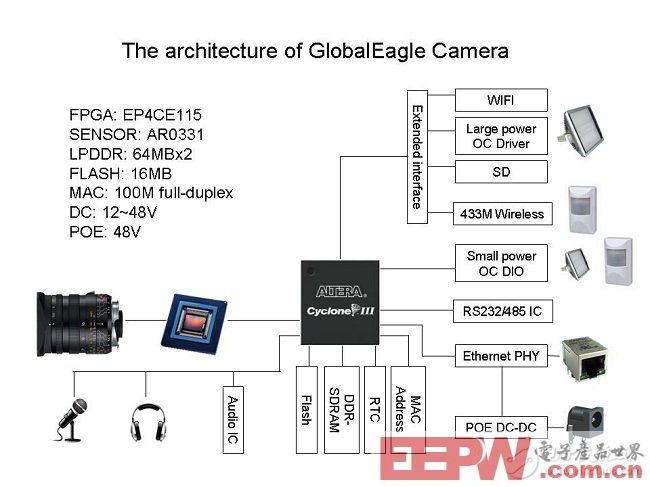

高清低码流H.264摄像机的结构简图如下:

图1 高清低码流H.264摄像机的结构图

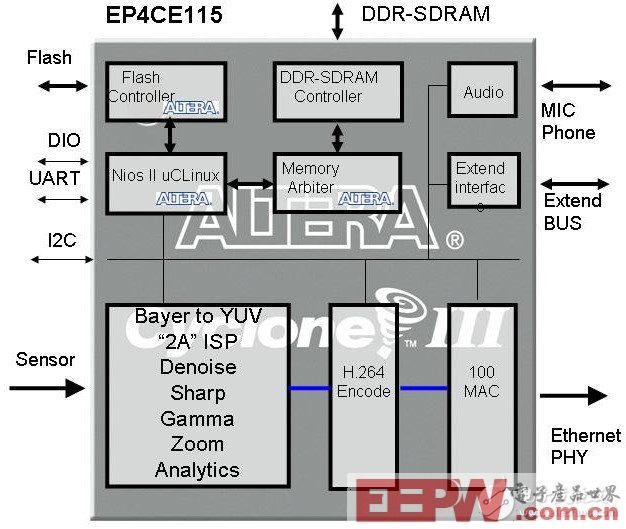

FPGA的内部结构如下图所示:

图2 FPGA的内部结构图

FPGA的选用

在高清低码流H.264摄像机的结构中,除了图像传感器、存储器、电源和模拟接口外,所有的功能如图像处理、H.264编码、协议处理、参数管理、媒体流发送等都由FPGA实现,FPGA就是高清低码流H.264摄像机的 SoC;目前世界上FPGA的生产商只有几个,可选择的产品也不多,要用FPGA实现高清低码流H.264摄像机的SoC,选择一款合适的FPGA非常重要,FPGA的选择主要考虑三方面的因素:速度、成本和结构;每个FPGA生产商都有多个FPGA系列,每个系列的速度、性能和价格都不同,要使高清低码流H.264摄像机SoC的成本尽可能低,应该选择成本最低的系列,像我们选择的FPGA是Altera公司的CYCLONE IV系列,型号是EP4CE115F23C8,CYCLONE IV是低成本系列,在同样是低成本系列的FPGA中,CYCLONE IV的速度是最快的; FPGA的结构对图像处理也很重要,尤其是存储器和乘法器的数量,H.264算法是以宏块为单位,在处理过程中必然会涉及到宏块的输入输出和缓存,1个宏 块的数据为384字节(256字节亮度数据和128字节色度数据),如果考虑到输入输出和处理的并行,必须设置双份,即768字节,用CYCLONE IV的1个M9K存储块正好,从上面的分析可以看出适合图像处理的FPGA对内部存储器的要求是存储块容量小(如1KB)、存储块数量多,另外,对乘法器的要求也是数量多;在我们选择FPGA的时候,CYCLONE IV是在所有低成本FPGA中有最大的存储器逻辑比和乘法器逻辑比,很适合做图像处理。

图像传感器的选择

为 了满足1280x720x25fps的要求,只需要选择百万像素的传感器就可以了,我们最终选择了300万像素的AR0331,还可以实现 1920x1088x11fps,在实现1280x720x25fps时还有电子PTZ功能,AR0331还有宽动态功能,便于摄像机以后扩充宽动态功 能。

外部存储器

外部存储器有2片LP DDR SDRAM和1片串行FLASH,串行FLASH用于存储FPGA的配置数据和NIOS的数据程序,1片LP DDR SDRAM用于存储图像数据和编码结果,1片LP DDR SDRAM用于NIOSII运行ucLinux。

FPGA实现的功能

FPGA作为高清H.264摄像机的SoC实现的功能如下:

① 图像处理

● 边缘检测RAW插值计算

简单的RAW插值计算会造成边缘模糊,增加边缘检测判断可以避免造成边缘模糊;

● 3D滤波

从图像传感器出来的图像包含有噪声,去噪同时在帧间和帧内进行;

● 2D锐化

由于镜头等因素影响,从图像传感器出来的图像需要锐化才能清晰;

● GAMMA校正

从图像传感器出来的图像灰度不正确,需要做GAMMA校正,获得正确的灰度;

● 自动曝光控制

根据亮度条件调节适合的曝光参数;

● OSD显示

可以叠加2048位图像,图像以宏块为单位,结构可以有128x1、64x2、32x4、16x8、8x16、4x32、2x64、1x128等选择,在屏幕的位置可以设置;

● 区域管理

可以定义隐私区域、运动检测区域等;

② 编码处理

● 编码格式

用H.264 main profile with cabac算法编码,可以提高压缩率,减少码流;由于完全实现H.264的全部算法需要大量的资源,需要很大容量的FPGA,这是不现实的,如我们用1个测试序列做过测试,2个参考帧比1个参考帧的压缩率提高了5%,但是2个参考帧的处理要比1个参考帧的处理需要多远不止5%的资源,对于一些很复杂而压缩 率提高不多的方法我们暂时不采用,降低码流是1个系统性的工作,需要从多个环节考虑;另外我们必须保证算法的准确,以免在解码端产生误差;

● 编码能力

最大为1280x720x25fps,如果需要同时编码多路码流,需要考虑3路码流的每秒宏块编码数量之和不能大于90000,如 1280x720x23fps+320x180x23fps,1136x640x24fps+568x320x24fps+284x160x24fps 等;

● 图像质量控制

编码量化参数调整范围:24~41,值小码流大,图像质量好,值大码流小,图像质量差;

● 码流控制

码流控制方式为CBR,控制平均码流;

③ 网络处理

● 网络速度峰值

目前网络接口使用全双工100M以太网,由于图像的编码数据量是不均匀的,I帧的编码数据量大,P帧的编码数据量小,所以数据量呈脉冲式分布,在传输I帧的 编码数据时尽量采用大的网络速度有利于减少延迟,但是应该考虑到ADSL的承受能力,可以设置1~70M的网络速度峰值;

● 码流均值

码流均值是1秒种传送的数据量,可以设置16Kbps~8128Kbps的码流均值;CBR的码流控制方式就是根据码流均值来进行的;

● 码流缓冲

由于编码数据量呈脉冲式分布,当编码的数据产生速度高于网络速度峰值时,编码数据就需要缓存在LP DDR SDRAM,否则就会丢失;

● 协议

TCP、RTP、RTSP、DHCP、NTP、HTTP、FTP、SMTP和DDNS;

④ 管理

● NIOS II

NIOS II是内置CPU,运行ucLinux,负责媒体流数据的缓冲和打包发送;

● 参数(通过WEB提供)

接收参数设置和更新,保留2份参数,1份是出厂时的参数,1份是实际使用的参数,在正常加电时实际使用的参数起作用,按复位键时出厂时的参数起作用;

● 升级(通过WEB提供)

FLASH里面保存两个配置数据,1个是出厂时的配置数据,1个是升级后的配置数据,当按复位键和升级配置数据加载失败时按出厂时的配置数据进行加载,否则按升级配置数据加载;

● 报警接口(通过WEB提供)

提供报警信号的上传功能;

⑤ 音频

支持双向64kbits ALaw和16kbits/32kbitsADPCM的收发,声音侦测。

5. 结束语

用FPGA作为SoC的高清低码流H.264摄像机已经完成设计,达到设计目标,视频质量清晰流畅,完全满足智能手机作为监控终端的要求。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论