采用高性能SRAM提高DSP密集型应用的性能

军事与国防应用极大地受益于数字信号处理器(DSP),其广泛应用于雷达、软件无线电(SDR)、灵巧弹药与目标探测系统、电子战应用、飞机成像以及众多其它应用。DSP借助其完美架构提供的精确处理能力可以显著提高性能。关键DSP功能包括实时信号处理、超高吞吐量与可重编程功能。本文介绍了如何采用高性能四倍数据速率(QDR)SRAM而使整体DSP系统性能至少提高两倍(与使用SDRAM的传统方法相比)的方法。

本文引用地址:https://www.eepw.com.cn/article/247534.htm数字信号处理

数字信号处理包含把信号转换成数字形式后对其进行处理的方法,如:雷达处理。雷达系统基本上是产生可以通过定向天线馈送的脉冲。这些信号以光速传播,而其路径中的任何物体都会把一小部分的投射能量反射回雷达接收天线。计算发送和接收信号的差别可以了解物体的距离与速度。

DSP是雷达系统的基础,可用于多种功能,如:脉冲压缩、信号滤波和脉冲调制。没有DSP,雷达系统就无法准确探测远距离的物体。DSP与通用的微处理器不同,因为它们适用于设计FFT和FIR等滤波器时最常用的快速数学计算(乘法与加法)类型。一般情况下FFT滤波器可用于域转换 – 从时域到频域或者相反,而FIR滤波器用于信号分离与恢复。这几种滤波器普遍存在于雷达设计中。

实现DSP有两种主要的硬件方法:可编程DSP处理器与现场可编程门阵列(FPGA)。在这两种方法中,DSP架构都非常适合DSP算法。

DSP处理器

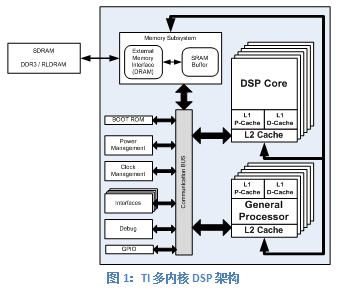

如图1所示的TI多内核DSP等DSP处理器采用专用硬件计算每个周期的乘法运算。现代DSP处理器的指令集允许编程人员在单个指令中指定多个并行运算,一般在主算术运算进行的同时一次或多次从存储器提取数据。另外,为了显著改善每个时钟周期的DSP性能,DSP架构目前包含并行运行的附加乘法器与加法器,从而可以在单个指令中编码并行运算。

评论