内置译码器的步进电机微步进驱动芯片A3977

1 引 言

随着微步进电机应用的日益广泛,其驱动电路的发展也相当迅速,各类控制芯片的功能越来越丰富,操作也越来越简便。A3977是一种新近开发出来、专门用于双极型步进电机的微步进电机驱动集成电路,其内部集成了步进和直接译码接口、正反转控制电路、双H桥驱动,电流输出2.5A,最大输出功率可接近90W。它主要的设计功能包括:自动混合模式电流衰减控制,PWM电流控制,同步整流,低输出阻抗的DMOS电源输出,全、半、1/4及1/8步进操作,HOME输出,休眠模式以及易实现的步进和方向接口等。其应用电路结构简单、使用及控制方便,有着极其广泛的应用价值。

2 A3977工作特点

大多数微步进电机驱动器都需要一些额外的控制线,通过D/A转换器为PWM电流调节器设置参考值以及通过相输入完成电流极性控制等。许多改进型驱动器仍然需要一些输入来调整PWM电流控制模式使其工作在慢、快或混合衰减模式。这就需要系统的微处理器额外负担8~12个需依靠D/A变换处理的输入端。如果一个系统需要如此多的控制输入,而且其微处理器还要存储实现其控制的时序表,这就增加了系统的成本和复杂程度。

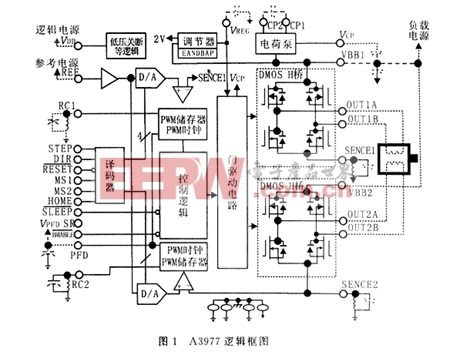

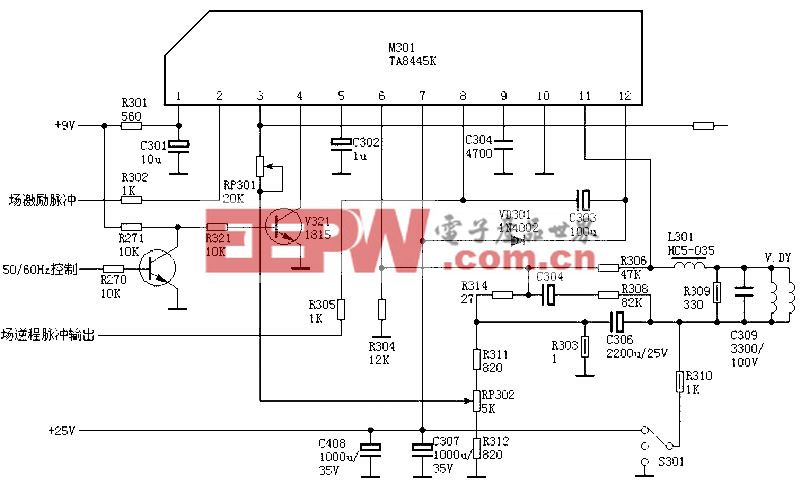

A3977可以通过其特有的译码器来使这些功能实现简单化,如图1所示,其最简单的步进输入只需“STEP”(步进)和“DIR”(方向)2条输入线,输出由DMOS的双H桥完成。通过“STEP”脚简单的输入1个脉冲就可以使电机完成1次步进,省去了相序表,高频控制线及复杂的编程接口。这使其更适于应用在没有复杂的微处理器或微处理器负担过重的场合。同时A3977的内部电路可以自动地控制其PWM操作工作在快、慢及混合衰减模式。这不但降低了电机工作时产生的噪声,也同时省去了一些额外的控制线。

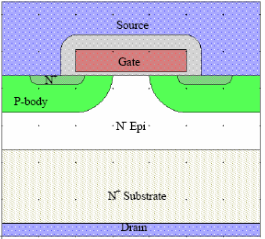

另外,其内部低输出阻抗的N沟道功率DMOS输出结构,可以使其输出达到2.5A,35V。这一结构的另一优点是,使它能完成同步整流功能。由于有同步整流流功能,既降低了系统的功耗,又可以在应用时省去外加的肖特基二极管。

A3977的休眠功能可以使系统不工作时的功耗达到最低。休眠时芯片的大部分内部电路,如输出DMOS、比较器及电荷泵等都将停止工作。从而在休眠模式时,包括电机驱动电流在内的总电流消耗在40μA以内。此外,内部保护电路还有利用磁滞实现的热停车、低压关断及换流保护等功能。

集成电路的主要特点:

(1)额定输出为:±2.5A,35V。

(2)低输出阻抗,源端0.45Ω,接收端0.36Ω。

(3)自动电流衰减检测并选择混合、快和慢等电流衰减模式。

(4)逻辑电平范围为3.0~5.5V。

(5)HOME输出。

(6)降低功耗的同步整流功能。

(7)内部低压关断、热停车电路及环流保护。

3 A3977引脚说明

A3977有两种封装:一种是44引脚铜标塑封(后缀为ED,A3977SED),另一种是28引脚带散热衬垫的塑封(后缀为LP,A3977SLP),其引脚功能说明如表1所示。

电荷泵CP1、CP2可以产生一个高于VBB的门电平,用来驱动DMOS源端的门。其实现方法是在CP1和CP2之间接一个0.22μF的陶瓷电容。同时VCP和VBB间也需要一个0.22μF的陶瓷电容作为一个蓄能器,用来操作DMOS的高端设备。

VREG是由系统内部产生,用于对DMOS漏端输出进行操作。VREG引脚须对地加一个0.22μF的陶瓷电容作为一个蓄能器,用来操作DMOS的高端设备。

VREG是由系统内部产生,用于对DMOS漏端输出进行操作。VREG引脚须对地加一个0.22μF的电容去耦。VREG是受内部的电平调节器控制的,发生故障时其输出是被禁止的。

RC1和RC2引脚是为内部PWM电路提供固定截止时间的。A3977的内部PWM控制电路是用一个脉冲来控制器件的截止时间的。而这个脉冲的—84—截止时间toff就是由RC1和RC2引脚对地所接的电阻RT和电容CT决定的,即:

toff=RT CT

式中,电阻RT和电容CT的取值范围分别为12~100kΩ及470~1 500pF〉

另外,除了可以为内部PWM控制提供截止时间外,CT还为比较器提供了关断时间tBLANK。A3977的设计要求当其输出由内部电流控制电路切换时,电路取样比较器的输出是被禁止的。从而可以防止对过电流检测作出误判断。tBLANK的取值为:

tBLANK=1400CT

ENABLE输入为低电平有效,它是DMOS输出的使能控制信号。RESET输入也是低电平有效,当其为低电平时,DMOS的输出将被关断,所有的步进逻辑输入也将被忽略直至其输入变高为止。

4 基本功能说明及应用电路

由于采用了内置译码器技术,A3977可以很容易的使用最少的控制线对步进电机实施微步进控制。具体功能实现如下:

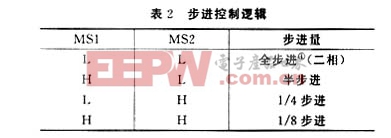

(1)步进控制:步进控制信号有步进输入(STEP)、步进模式逻辑输入(MS1,MS2)以及方向控制信号(DIR)。每一次上电或复位(RESET=0)后,在内置译码器的作用下将H桥的输出预置到HOME输入所对应的输出状态,然后当STEP输入的上升沿到来后,内置译码器将根据步进逻辑的输入值(步进模式见表2)控制H桥的输出,使电机在当前步进模式下产生1次步进。

步进的方向由DIR的输入逻辑控制,其高、低电平分别控制双相电机正反转。

注:①全步进转过的角度为45°。

(2)内部PWM电流控制:每一个H桥都有一个有固定截止时间的PWM电流控制电路,以限制其负载电流在一个设计值。初始时,对角线上的一对源接收DMOS(一对上下桥臂)处于输出状态,电流流经电机绕组和SENCE脚所接的电流取样电阻(见图1)。当取样电阻上的压降等于D/A的输出电压时,电流取样比较器将PWM锁存器复位,从而关断源驱动器(上桥臂),进入慢衰减模式;或同时关断源接收驱动器(上下桥臂)进入快或混合衰减模式,使产生环流或电流回流至源端。该环流或回流将持续衰减至固定截止时间结束为止。然后,正确的输出桥臂被再次启动,电机绕组电流再次增加,整个PWM循环完成。

其中,最大限流Imax是由取样电阻RS和电流取样比较器的输入电平VREF控制的:

Imax=VREF/8RS固定截止时间toff的计算如上所述。

(3)电流衰减模式控制:A3977具有自动检测电流衰减及选择电流衰减模式功能,从而能给微步进提供最佳的正弦电流输出。电流衰减模式由PFD的输入进行控制,其输入电平的高低控制输出电流处于慢、快及混合衰减模式。如果PFD的输入电压高于0.6VDD,则选择慢衰减模式。如果PFD的输入电压低于0.21VDD,则选择快衰减模式。处于二者之间的PFD电平值将选择混合衰减模式。

其中混合衰减模式将一个PWM周期的固定截止时间分为快、慢两个衰减部分。当电流达到最大限流Imax后,系统将进入快衰减模式直至SENCE上的取样电压衰减至PFD的端电压VPFD。经过tFD的快衰减后,器件将切换至慢衰减模式直至固定截止时间结束。

其中,器件工作在快衰减模式的时间tFD为:

tFD=RTCrln(0.6VPFD/VPFD)

(4)同步整流控制:同步整流控制是由SR的逻辑输入控制的。当SR输入为低电平时,同步整流功能将被启动。此期间,当检测到电流为零值时,可通过关闭同步整流功能来防止负载电流反向,从而防止了电机绕组反方向导通。而当SR输入为高电平时,同步整流将被禁止。

(5)休眠模式:当SLEEP引脚输入为低电平时,器件将进入休眠模式,从而大大降低器件空闲的功耗。进入休眠模式后器件的大部分内部电路包括DMOS输出电路、调节器及电荷泵等都将停止工作。当其输入为高电平时,系统恢复到正常的操作状态并将器件的输出预置到HOME状态。

(6)典型应用电路:其典型应用电路如图1所示,可见其应用电路是非常简单的,其正常工作时仅需5个逻辑输入即可。

5 应用注意事项

(1)PFD引入端应加一个0.1μF的电容去耦。

(2)布线时应布一个较厚的地层,最好在本器件周围布上星形地。

(3)最好将芯片直接焊接在线路板上。

(4)为VBB引脚加一个大于47μF的电解电容去耦(越靠近芯片越好)。

(5)为保证输出电流取样的精确,最好使取样电阻有自己单独的地,并将其连到器件周围的星形地

上,而且引线越短越好。

(6)当系统由休眠模式退出后,最少要延迟1ms才可以输入步进命令,从而为驱动DMOS的电荷泵复位提供充裕的时间。

评论