基于FPGA的视频图像分割技术设计与应用

数字硬盘录像机是一种性价比很高的视频监控解决方案,具有对图像/语音进行长时间录像、录音、远程监控和控制的功能,集合录像机、画面分割器、云台镜头控制、报警控制、网络传输等功能于一身,是目前市面上视频监控系统的首选产品。在DVR系统中,需要在一个现实设备上同时显示多个监控画面,这样可大大节省资源并便于工作人员监视,本文研究的内容就是这种图像分割技术在FPGA上的实现。

FPGA是20世纪80年代由美国Xilinx公司首先推出的,它具有性能高、规模大、可重复编程、开发投资小等优点,在现代电子产品设计中应用广泛。FPGA具有极高并行度的信号处理引擎,提供高性能的信号处理能力。在本设计中,就是要利用FPGA的高速性能对多路视频信号进行处理,从而简化硬件结构,提升DSP性能,使单片DSP实现16路CIF图像实时编解码成为可能。

1 图像分割与合成

1.1视频标准

FPGA处理的视频数据由专用解码芯片Tw2815输出,符合ITU.RBT.656标准。ITU.RBT.656标准是在国际电信联盟无线电通信部门656.4号建议书中提出,全称是工作在ITU.RBT.601建议(部分A)的4:2:2级别上的525行和625行电视系统中数字分量视频信号的接口。实施这样的标准是为了在525行和625行两者间提供一种世界范围兼容的数字化方法。数据信号编码成8比特二进制信息形式,格式如图1所示。

由图1可知ITU.RBT.656并行接口除了传输4:2:2的YCbCr视频数据流外,还有行、列同步控制信号。一帧数据由525行(NTSC制式)或625行(PAL制式)、每行1728个字节的数据块组成。每行数据中,有4个字节的EAV和SAV信号,前3个字节是前导数据,最后一个字节中包含本行数据信息。EAV/SAv包含了关于同步的所有信息。

1.2 割与合成原理

视频图像合成基于像素域,即将多路压缩的源视频编码数据进行解码,将解码后的YUv(或RGB)数据按照一定线性规则进行排列,合并成一路ⅥⅣ(或RGB)数据,再将合并后的视频数据进行编码12J。ITU.RBT.656标准YCbC,(4:2:2)格式中4:2:2的含义为Y信号与Cb、C,信号的数量比为4:2:2,即在有效视频数据区域,每4个字节为一个宏像素点,其中包含2个Y信号,1个Cb信号和1个Cr信号。

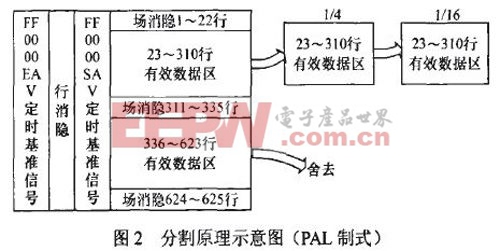

要实现4画面及16画面显示功能,就是要以宏像素为单位对原画面像素按照1/4(或1/16)的比例进行抽取,如图2所示(以PAL制式一帧数据为例)。

通过上面的方法可以得到各视频通道1/4(或1/16)画面数据接下来的任务是将画面合成并传输给DSP做编码处理。通过实验得到:对于TMS320DM6467芯片的VPIF(视频设备接口)来说,只要输入视频数据有效数据行内从EAV到SAV之间的字节数为一定值(可由DSP内部寄存器设置),且行数满足对应制式要求,DSP就能将其识别为一帧有效数据。这样就能得到图3所示的第一种画面合成方法。这种方法虽然可行,但是可以看到,在有效数据区中每一行都由多个通道数据组成,在从内存读取数据时通道切换频繁。会给编码和调试带来困难。

评论