如何在FPGA和ASIC设计中结合高速USB功能

USB提供的吞吐量足够大,适合高带宽应用,如硬盘驱动器和扫描器。事实上,对于大部分计算机外设,如键盘,鼠标,PDA,游戏键盘,操纵杆,扫描仪,数码相机,打印机,USB已经是互连标准。

除了简单的电脑外围设备,FPGA应用也广泛存在,其可以受益于高速USB接口的增加。数字信号示波器、心电图、摄像机和数据采集系统是其中的一些例子。将USB接口添加到设备里将会大大扩展其能力。例如,在数据记录系统中(如数字储存示波器和心电图),得到实时数据可以通过主机实时传输,也可以通过网络传输这个数据,如图1所示。对于远程数据采集应用,将数字记录仪设备通过USB连接到主机也可以使设备进行远程控制,主机可以位于几英里以外,通过网络连接到USB主机。本文将探讨其设计方法,可以在FPGA或ASIC系统中实现高效高速USB 2.0接口。

图1 基于USB的分布式数据采集系统

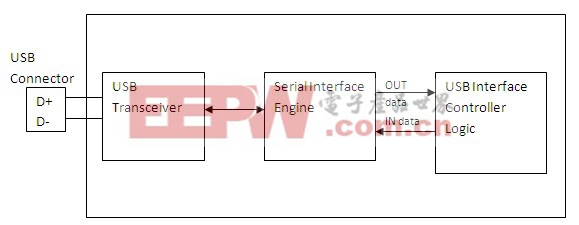

在介绍整合通用串行总线接口到FPGA或ASIC系统的各种方法之前,我们需要了解一下典型USB系统的工作原理。典型的USB系统由收发器,串行接口引擎(SIE),和接口控制器构成,如图2所示。

图2 典型的USB系统

收发器实现了USB协议的物理层。收发器形成了主设备和从设备之间数据连结的两端。USB接收器会有差分和单端两种输出。SIE进行串行数据的编码和解码,位填充,错误校验和其他信号级处理任务。它还将并行数据转换成串行数据,反之亦然。SIE应该连接到智能master,其通过控制端点相应主设备请求实施高级USB协议。master也将实现器件功能所需的应用级任务。

在这篇文章中,我们将讨论三种不同的方法,实现USB接口添加到FPGA或者ASIC系统。

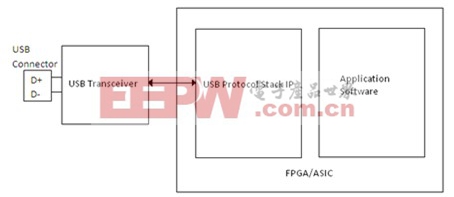

使用USB协议栈知识产权(IP)及外部收发器

在第一种方法中,我们可以在FPGA或ASIC中实现SIE(见图3)。

图3 FPGA + USB协议栈IP + USB收发器

评论