利用FPGA解决手持设备MPU功耗问题

为应对上述挑战,越来越多的设计人员开始使用FPGA进行手持产品的开发。FPGA的功能日益强大和丰富,而门数、面积和频率也在不断增加。FPGA的开发和周转时间要比定制ASIC短得多,可重复编程的额外优势使得FPGA成为手持嵌入式系统领域中颇具吸引力的解决方案。在基于ASIC或FPGA的设计中,设计人员必须认真考虑某些性能标准,他们面临的挑战主要体现在面积、速度和功耗方面。

与ASIC一样,供应商在FPGA设计中也需要应对面积和速度的挑战。随着门数不断增加,FPGA需要更大的面积和尺寸来适应更多的应用,设计工具需要采用更好的算法以便更有效地利用面积。不断演进的FPGA技术也给设计人员带来一系列新的挑战,电源利用率就是其中之一,这对于为手持或便携式设备设计基于FPGA的嵌入式系统来说是急需解决的问题。

嵌入式系统中的FPGA

典型的嵌入式系统由处理器、存储器、包括USB、SPI、I2C在内的标准接口以及液晶显示器、音频输出等外设组成。设备的核心仍是处理器和处理器接口,它们通过板载连线连接到各个外设。系统性能主要取决于处理器性能,而处理器通常具有非常标准的架构,因而不容易定制。

有时处理器可能忙于处理来自低速外设的信息,虽然在这种情况下处理器使用率可能达到100%,但并不是在做以微处理器为中心的事务,而是工作在特别低的性能水平。不管其内核频率是多少,微处理器必须等待来自低速时钟的数据。这也会导致较高的功耗,因为处理器的利用率是100%。其结果将缩短电池寿命,并且需要更大的散热器或风扇进行冷却,最终影响整个系统的可靠性。

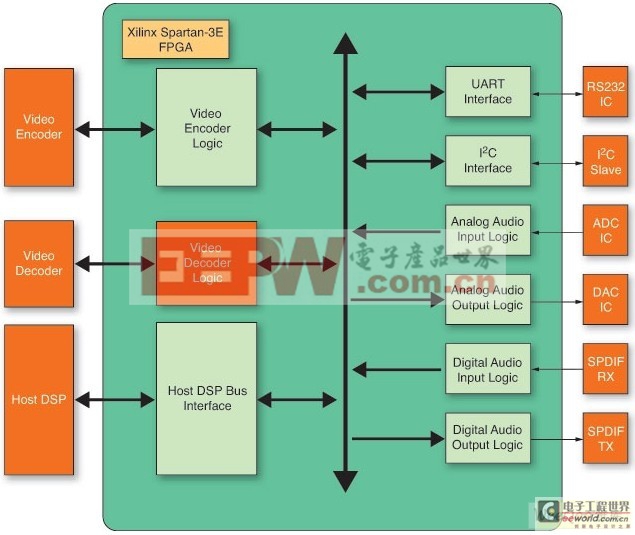

于是,FPGA在这方面开始发挥重要作用,因为它们能从处理器卸载许多外设交互任务。如图1所示,利用标准千兆TCP/IP网络实现的未压缩音视频数据流的嵌入式分布系统。它有一个专用DSP处理器,这个处理器通过一个标准总线接口与赛灵思的FPGA相接,FPGA再连接到各个低速外设。

图1:用于音频/视频分布系统的FPGA架构。

作为启动开发套件,这个FPGA通过I2S接口连接12位的PCM音频输入和12位的PCM音频输出;它还连接视频编码器和解码器,并与I2C从器件和RS232器件进行通信;连接到FPGA的通用I/O很少。与处理器相连的标准总线工作在高速的66MHz,而音频外设工作在低速的1.182MHz;UART和I2C串行接口分别工作在56.6kHz和100kHz。由于数据传输发生在多个时钟域,因而只有处理器能配置数据流。

在这种情况下,处理器不再与低速外设交互,而由FPGA从低速的PCM ADC音频器件读取数据,并将数据存放在FPGA的内部缓存中。处理器可以周期性地从这个缓存读取数据,或者当缓存中有足够数据时,由FPGA向处理器发送一个中断。这样,处理器就有更多的时间执行以处理器为中心的必要工作,在空闲时则进入睡眠模式。

评论