基于FPGA的监测数字示波器设计

摘要:在核监测中,常将各种传感器输出的信号通过A/D转换器转换为数字信号,然后利用数字信号处理技术对各种核信号进行数字处理。为了准确测量核信号数字波形的各种参数,对基于FPGA双口RAM的数字示波器进行了设计和测试分析。实验表明,该数字示波器能准确获取核信号的数字渡形及各种参数的值,可对核信号的波形进行录制、回放和精确分析,为核监测及其仪器准确设计提供有力的保证。

本文引用地址:https://www.eepw.com.cn/article/235057.htm福岛核事故促进了核监测仪器的飞速发展。在核爆监测中,需对核辐射的各种信号如光辐射、放射线沾染、冲击波、电磁辐射等进行测量,通过测量这些信号的时间、幅度和信号波形信息,判断核爆炸的时间、位置、方式和当量等。为了将信号存储、分析及各种数学处理,需要将核信号转换为数字信号。基于FPGA的数字存储示波器可以实现核信号的采集、存储及各种处理,获取核信号的各种参数,输出报警信息,再将获取的信号通过GPRS、北斗1和数传电台等多种方式传送至指挥中心,为核监测决策提供数据支持。下面就基于FPGA双口RAM的数字存储示波器进行设计研究。

1 FPGA简介

现场可编程门阵列(FPGA)是在专用集成电路(ASIC)的基础上发展起来的一种新型逻辑器件,是当今数字系统设计的主要硬件平台。其主要特点就是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。在修改和升级时,不需额外地改变PCB电路板,只要在PC机上修改更新程序,使硬件设计工作成为软件开发工作。

通过编程可以立刻把一个通用的FPGA芯片配置成用户需要的硬件数字电路,因而大大加快电子产品的研发周期,降低研发成本,缩短产品上市时间。FPGA具有高密度(一个器件内部可用逻辑门可达数百万门),运行速度快(管脚间的延时小,仅几个纳秒)的特点。用FPGA设计数字电路可以简化系统设计,缩小数据规模,提高系统的稳定性。FPGA不仅可以解决电子系统小型化、低功耗、高可靠性等问题,而且开发软件投入少、芯片价格不断降低,这使得FPGA占有越来越多的市场,特别是对小批量、多品种的产品需求,使FPGA成为首选。同时FPGA的Inte llectual Property(IP)越来越被高度重视,带有IP内核的功能块在ASIC设计平台上的应用日益广泛。尤其是FPGA很方便设计各模块并行处理,极大地提高信号处理速度。由于FPGA的上述优点,基于FPGA的各种仪器设计技术得到了越来越广泛的应用。

2 基于双口RAM的数字示波器设计

2.1 基于双口RAM的数字示波器的设计原理

核辐射探测传感器将核辐射的各种信号转换为电信号,该电信号为模拟信号,然后放大、成形等电路对模拟信号进行适当的调理,高速A/D转换器将模拟信号转换为数字信号,FPGA对该数字信号进行数字滤波、存储等处理。基于双口RAM的数字示波器原理图如图1所示。

2.2 模/数转换电路

要对核信号进行精确的数字分析处理,就需要对核信号进行精确的数字取样,取样频率越高,取样结果越准确。AD9244是Analog Devi ce公司生产的14位高速高精度模/数转换器,具有750 MHz输入带宽,采用流水线技术,每个脉冲可进行一次A/D变换,最高允许抽样速率达到65 MHz。它专门应用于峰峰值小于2 V的小信号模/数转换系统,其最大的特点是体积小、功耗低、精度高。输入模拟量在-1~1 V之间时,溢出位为0,输入模拟电压为-1 V时,输出14位数字量为00000000000000;输入模拟电源为0 V时,输出数字量为10000000000000;输入模拟量为1 V时,输出数字量为11111111111111。输入模拟量低于-1 V时,溢出位为1,输出数字量为00000000000000;输入模拟量高于1 V时,溢出位为1,输出数字量为11111111111111。A/D取样示意图如图2所示。NaI(T1)闪烁体探测器核脉冲信号经放大整形后输出近高斯波形模拟信号,再经8138转换为差分模拟信号进入AD9244,FPGA输出50 MHz时钟信号ADC_CLK到AD9244作为ADC的时钟源,AD9244则输出50 MHz 14位数字信号及1位溢出位信号到FPGA,完成模拟核脉冲信号的高速采样。每个ADC_CLK脉冲,ADC完成一次模/数变换。

2.3 双口RAM IP核定制

存储核监测数字信号既可以使用FPGA内部的FIFO存储器,也可使用内部RAM存储器。FIFO存储器控制简单,使用方便,但要访问存储数据的中间数值不很方便;RAM存储器使用更灵活,可以利用地址来处理RAM中的任何一个数据。在FPGA内部,RAM有两种类型,分别是BlockRAM和Distribute RAM。其中Block RAM为硬件RAM,集中分布在FPGA内的一个区域,利用Block RAM存储数据时,不占用其他逻辑资源。Distribu te RAM是由FPGA内的逻辑元件综合成的存储单元,广泛分布在FPGA的各个区域,离逻辑单元电路较近,用于存储各逻辑电路处理的信号。数字示波器存储的波形数据量较大,所以在双口RAM采用Block RAM实现。

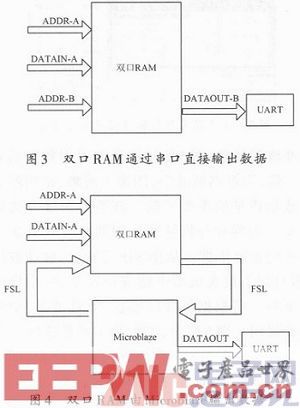

AD9244输出的数字信号为14位,所以RAM的数据宽度设置为16位,双口RAM数据读、写可采用相同的时钟控制;波形存储深度设定为1 024,即双口RAM存储1 024个采样点数据,所以双口RAM存储器共占用16 Kb RAM空间。由于核仪器工作在高辐射污染区,人员一般不能进入,通信一般采用无线通信方式,所以数据常采用串口通信方式。双口RAM数据直接经串口输出的原理图如图3所示。双口RAM数据经FSL总线由Microblaze处理器输出原理图如图4所示。A口用于RAM信号存储,数据宽度16位,深度1 024。B口用于RAM数据输出,若用ISE编写串口程序,B口数据宽度为8位,深度2 048;若采用PLB或FSL总线IP核方式,B口数据宽度定制为16位(16位RAM数据加载到32位总线的低16位上,总线高16位补零),深度为1 024。

模拟信号相关文章:什么是模拟信号

fpga相关文章:fpga是什么

数字滤波器相关文章:数字滤波器原理

评论