基于0.5μm BCD工艺的欠压锁存电路设计

随着集成电路技术的发展,对电源管理芯片的开关频率、传输延迟、稳定性、功耗等各种要求越来越高,以保证电源电压在波动的情况下能够可靠的工作。

一般的电源芯片上电启动时,电源会通过输入端的等效电阻和电容对其充电,使得电源芯片的电压逐步上升,直到电压上升到芯片的开启电压时电路正常工作。然而若系统的负载电流较大,有可能把电路的电压拉低到开启电压以下,出现一开启就关断的情况。为了保证电路正常进入启动状态并且稳定工作,同时也为了电路工作时电源电压的波动不会对整个电路和系统造成损害,一般使用所谓的欠压锁存(Under Voltage LockOut,UVLO)电路对电源电压实时监控和锁存。

传统电源管理类集成电路的欠压锁存电路的设计思路都是由比较器、带隙基准参考电压和一些逻辑部件构成的,其存在响应速度跟不上,功耗大,电路面积太大等问题。针对这些问题,设计一种新的欠压锁存电路,在不使用额外的基准电压源和比较器以及复杂的数字逻辑的情况下,能够达到UVLO的各项指标。它最主要的特点就是具有简单的电路结构、高的反应速度、低的温度敏感性和精准的门限电压,同时版图面积节省、功耗较低。

1 应用框图与传统电路结构

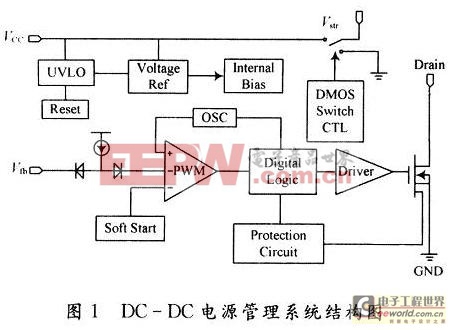

图1是DC-DC电源管理系统结构图。引脚Vstr直接与220 V交流整流器相连,最大耐压650 V。只要芯片一上电,UVLO电路就实时地对电源电压进行监控。芯片刚上电时,电流通过引脚Vstr给引脚VCC外接电容充电,当充电到芯片预置的开启电压Von时,UVLO电路输出电平发生翻转,芯片内部电路开始工作,Vstr对地短路,芯片电源由辅助变压器对VCC外接电容充电供给。正如上所述,UVLO电路同时设置了一个关闭电压Voff(VoffVon),用于防止由于系统负载电流较大而引起的一上电就关断的情况。同时,由其他情况引起的电源电压波动导致芯片电压下降到Voff时,UVLO电平恢复,芯片不产生参考电源,所有逻辑操作都将被终止。

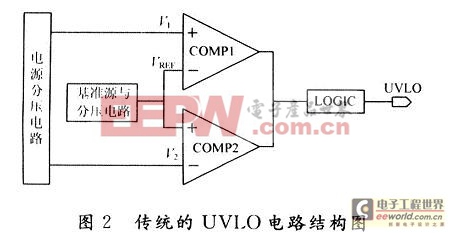

由此可见,UVLO电路实质上是一个迟滞电压比较器,它必须具备反应速度灵敏,门限电压稳定,滞回区间合理,温度漂移较低等特点。但是许多电源管理类集成电路的欠压锁存电路的设计思路都是由比较器、带隙基准参考电压和一些逻辑部件构成的,如图2所示。不是响应速度跟不上,就是功耗太大,更重要的是这种电路使用带隙基准参考电压源和分压电路,太过于复杂,使得电路面积太大而不利于降低成本。

在此提出一种基于0.5μm BCD工艺的UVLO电路,在不使用额外基准电压源和比较器以及复杂数字逻辑的情况下,能够达到UVLO的各项指标,其最主要的特点就是具有简单的电路结构、高反应速度、低温度敏感性和精准的门限电压,同时版图面积节省、功耗较低。

2 电路工作原理

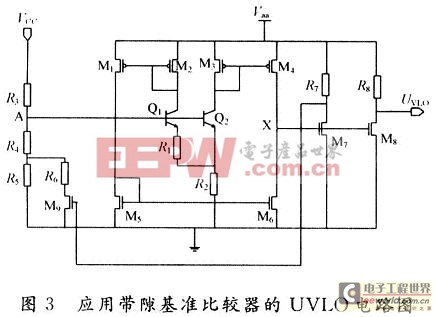

如图3为所设计的UVLO电路图。

晶体管Q1和Q2,电阻R1,R2利用了带隙基准原理组成的比较器,有些文献也把这种比较器称为带隙基准比较器。文献[4]给出了类似的电路拓扑结构,但是对于电路具体工作原理没有做出详细的解释。MOS管M2,M3为其提供有源负载,M1,M2,M3,M4,M5,M6组成镜像管,R3,R4,R5,R6和M9组成电阻分压网络,其中M9管的作用下面会详细介绍,R7,M7;R8,M8组成两级反相器,Vaa是由Vcc通过稳压二极管产生。

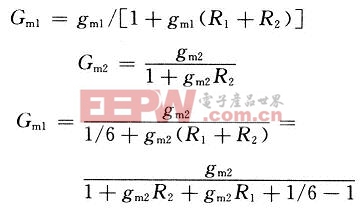

取晶体管Q1的发射区面积是Q2的6倍,那么两个晶体管的跨导关系是:

![]()

由于电阻R1,R2的射极反馈作用,所以晶体管Q1,Q2的等效跨导分别是:

一般情况下gm2R1》1,所以Gm1Gm2。于是,当芯片的电源电压Vcc波动时,晶体管Q1的集电极电流IC1比晶体管Q2的集电极电流IC2变化量要小。正是基于这种集电极电流变化量的快慢,带隙基准比较器以IC1为参考端来比较IC1和IC2大小。首先当VCC由低压逐步上升时分以下三种情况:

(1)当Vcc比正常供电低的情况下,由于Q1的等效跨导较Q2的跨导小,流过Q2的电流IC2比流过Q1的电流IC1小。如果M1,M2,M3,M4,M5,M6都处在饱和区,那么通过电流镜M1,M2,M5,M6镜像到M6管的漏电流ID6比通过电流镜M3,M4镜像到M4的漏电流ID4(ID4和ID6均指的是大小而不包含方向)大,这在同一条直流通路下是不可能的,这就驱使M6进入线形区,以保持和M4的漏电流相等。这样带隙基准比较器的输出X点为低电位,经反向后UVLO输出高电位从而关闭基准电源和锁存整个芯片。应当注意的是此时M9管处于导通状态。

(2)当VCC继续上升到接近Von时,流过Q1和Q2集电极电流近似相等,即IC1△IC2,那么这时所有镜像对管都处于饱和区且电流相等。由于PMOS导通电阻比NMOS导通电阻大2~3倍,选择Vaa=5 V。则X点电位大于M7的阈值电压,M7管导通且首先工作在饱和区,选择M7,M8管的宽长比相等,R7=R8,此时:

![]()

只要适当选择M7,M8管的宽长比和电阻R7,R8的大小,就能使得UVLO仍然输出高电平,从而达到关断基准电源和锁存整个芯片的目的。

(3)当VCC上升到大于Von时,由于Q2比Q1的跨导大,所以,IC2迅速超过IC。假设带隙基准比较器中各个镜像对管都处于饱和区,则同第二节(1)中的分析。同一直流通路上的电流ID6较ID4小,这是不可能的,所以这会驱使M4管进入线形区。这样,带隙基准比较器输出X点电位上升到高电平,经反相器反向后使得M9管关闭。A点电位进一步被拉升,从而确保UVLO输出为低电平,使得芯片正常工作。正是由于镜像对管对流过它们电流差异具有高度敏感性,所以这种UVLO电路反应速度很快。当VCC由高压慢慢变低时,同样也有三种情况:

①当VCCVoff时,同上一情况中的(3),IC1IC2,M4工作在线形区,M9工作在截止区,UVLO输出为低电平。

②当VCC下降到接近Voff时,类似于前面提到的(2),这时IC1△IC2,带隙基准比较器中的各个镜像管都工作在饱和区,X点的电位同样可以驱动M7管导通,且使其首先进入在线性区(注意同前面提到的(2)的区别),M9管关闭,UVLO输出仍为低电压。

③当VCC下降到Voff时,IC1>IC2,M6进入线性区,X点电位被拉低,经过反向器作用,M9管导通,此时进一步达到低压锁存的效果。应当注意的是此时的Von≠Voff。

从上面的分析可知,当晶体管Q1和Q2的集电极电流相等时,带隙基准比较器各个镜像对管都工作在饱和区,此时A的电压大小非常关键。设此时A点电压为VREF,Q1,Q2集电极电流为:

![]()

对于双极晶体管的基极发射极电压,有以下关系:

![]()

而IS∝SE,其中,是晶体管发射极面积。由于Q1的发射极面积是Q2的6倍,所以,式中:

由于VBE具有负的温度系数,而VT具有正的温度系数,只要适当选择电阻R1、R2的比值,就可以实现几乎零温度系数的带隙电压。现在再分别计算Von和Voff。

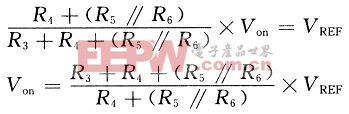

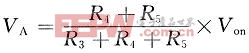

由上面分析可知,当电源电压VCC升高到尚未达到UVLO的开启电压Von时,UVLO输出高电平,且M9处于导通状态(忽略其导通电阻),此时A点电压为:

只有VA>VREF时,UVLO的电平才会翻转,这样就得到了开启电压的门限值Von,

一旦VCC>Von,M9管关闭,这时A点电压:

大于VREF,使得UVLO更稳定地输出低电平。同理,可以得出UVLO的关闭电压值Voff:

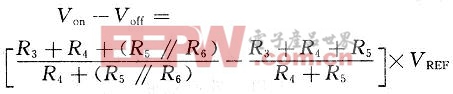

那么UVLO的滞回区间为:

3 电路仿真与分析

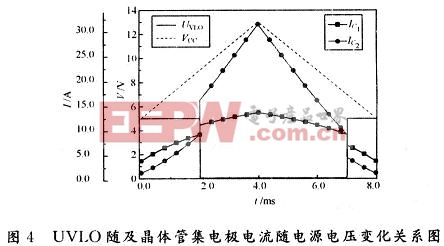

使用HSpice电路仿真软件在CSMC 0.5μm BCD工艺库下对UVLO电路进行仿真。由上面分析可知,UVLO电平翻转与晶体管Q1,Q2集电极电流变化速度快慢密切相关,所以对带隙基准晶体管上集电极电流变化做了如图4的仿真。从图4中可以明显看出,在2 ms以前,IC1>IC2,UVLO输出高电平。在2 ms时,两个晶体管的电流都急剧变大,但是由于Q2管的跨导比Q1管小,所以很快,IC1IC2,UVLO输出为低电平。下面可同理推出。

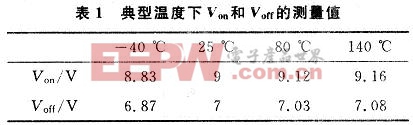

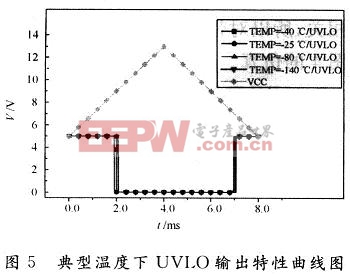

因为DC-DC芯片应用的温度范围比较大,而且工艺中的电阻、晶体管等受温度影响也比较大,所以在实际设计中,应当充分考虑到这点。在此对UVLO不同温度下进行仿真,尽可能把滞回区间的误差缩小到很小的范围内,以满足DC-DC芯片在宽温度范围内工作。表1和图5是对本文所设计的UVLO电路在-40℃,25℃,80℃和140℃下的仿真结果。从中可以看出,在25℃时,Von=9 V,Voff=7 V,滞回区间是2 V。在其他温度下的偏差最大也不超过0.2 V,可见其最突出的优势是可以在宽温度范围内工作而不失精度。

除此之外,当芯片发生欠压锁存时,芯片的功耗也是非常小的。这主要是因为当芯片发生欠压锁存时,芯片的其他部分都不工作,也就不消耗功率,UVLO电路的主要功耗是流过带隙晶体管和R3,R4,R5,R6电阻的电流所产生,只要适当地调节这些电阻阻值就可以把功耗降低到最低,但是考虑到版图的面积,实际仿真中的功耗可减小到150μW以下。

4 版图设计

使用CSMC 0.5 μm BCD工艺技术,对UVLO电路设计版图。由于利用带隙基准原理,在要求精度较高的情况下,设计时应注意UVLO模块与其他模块隔离。与传统的UVLO电路相比,最显著的提升就是版图面积大大缩小,只要工艺中包含高阻值的电阻类型,这种优势就更为突出。

5 结 语

在此针对DC-DC电源管理系统所必须的欠压所存功能,详细介绍一种新的改进UVLO电路,相对于传统的UVLO电路,它最突出的优点是不使用额外的带隙基准源和复杂的数字逻辑,因此节省了芯片面积。HSpice仿真结果表明,它在-40~+140℃范围内最大失真不超过2 %,因此可以在宽温度范围内工作。基本适用于各种类型的电源管理类芯片,对工艺要求也不高。

评论