基于共享技术的电荷泵电路

摘 要:为了减少芯片面积,提高电荷泵的增益,提出一种基于共享技术的电荷泵电路。通过改变两个子电荷泵的串并连接关系,既可以产生一种电压较高而电流驱动能力较小的负高压,也可以产生一种电压较低但是电流驱动能力很大的负高压,这不仅满足了系统在编程和擦除时对高压的不同需求,而且还节省了大约50%的芯片面积。电荷泵电路还采取了对其中P型MOS管的衬底电压进行动态控制的方法。模拟结果表明,该电荷泵的增益提高了大约14%。该电路特别适用于需要两种以上负高压以完成编程和擦除操作的快闪存储器。

关键词:电荷泵;共享;快闪存储嚣;驱动能力

电子可擦除可编程存储器(electrically-erasableprogrammable read-only memory,EEPROM)和快闪存储器在编程和擦除操作时都需要高压,因此电荷泵电路在单电源的嵌入式存储器芯片中扮演着极其重要的作用,其功耗,面积和在低电源电压下的工作能力等直接影响到整个存储芯片的性能。而且在实际应用中,一个存储器芯片内部一般会需要不止一种正高压和负高压,所以系统中会需要多个正高压电荷泵和负高压电荷泵,这使得电荷泵所占芯片面积超过整个存储器芯片中外围电路的一半。对于采用带带隧穿热电子注入(band-to-bandtunneling induced hot electron,BBHE)进行编程的p沟道DINOR(p-channeldivided bit-line NOR)结构的快闪存储器,它需要至少一个正高压电荷泵和两个负高压电荷泵。对于采用源极诱导带带隧穿热电子注入(source induced band-to-band hotelectron_,SIBE)方式进行编程的新型快闪存储器,系统总共需要2个正高压电荷泵和3个负高压电荷泵。

由于电荷泵电路所占据的面积很大,尤其当电源电压逐渐从5V降到1.8V甚至1.2V时,要产生足够的高压,电荷泵必须要增加级数或者增大耦合电容的大小,这使得电荷泵电路占据的面积不断增加。因此电荷泵的共享技术在减少芯片面积上非常重要,但是这要么会增加工艺的难度,要么使得电路结构变得非常复杂。

本文通过改变电荷泵的串并连接关系,在不增加任何工艺难度和电路复杂度的情况下,实现了电荷泵的共享,使得电荷泵电路所占据的面积大大减少。

1 共享技术电荷泵的结构和工作原理

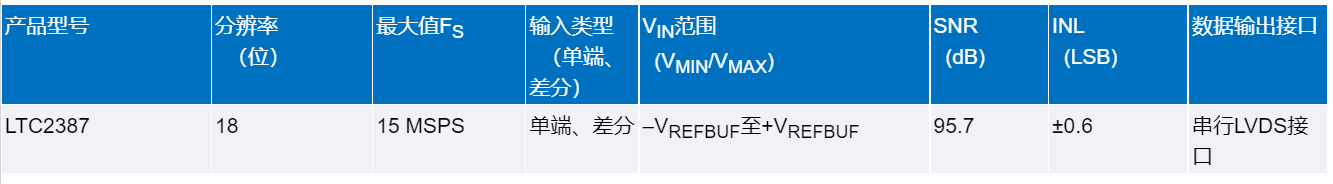

表1给出SIBE结构快闪存储器的典型操作模式,其中编程时加到位线上的-3.3 V高压需要提供大于100μA的驱动能力,以实现多位数据同时编程。

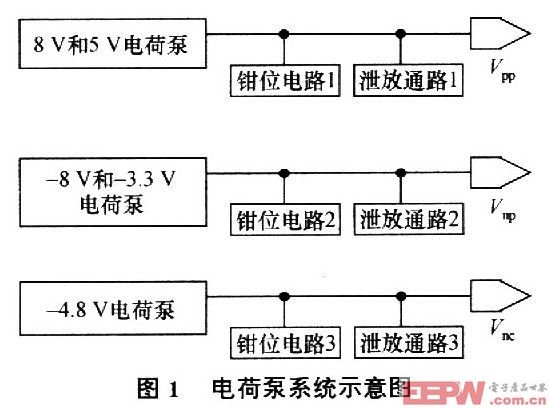

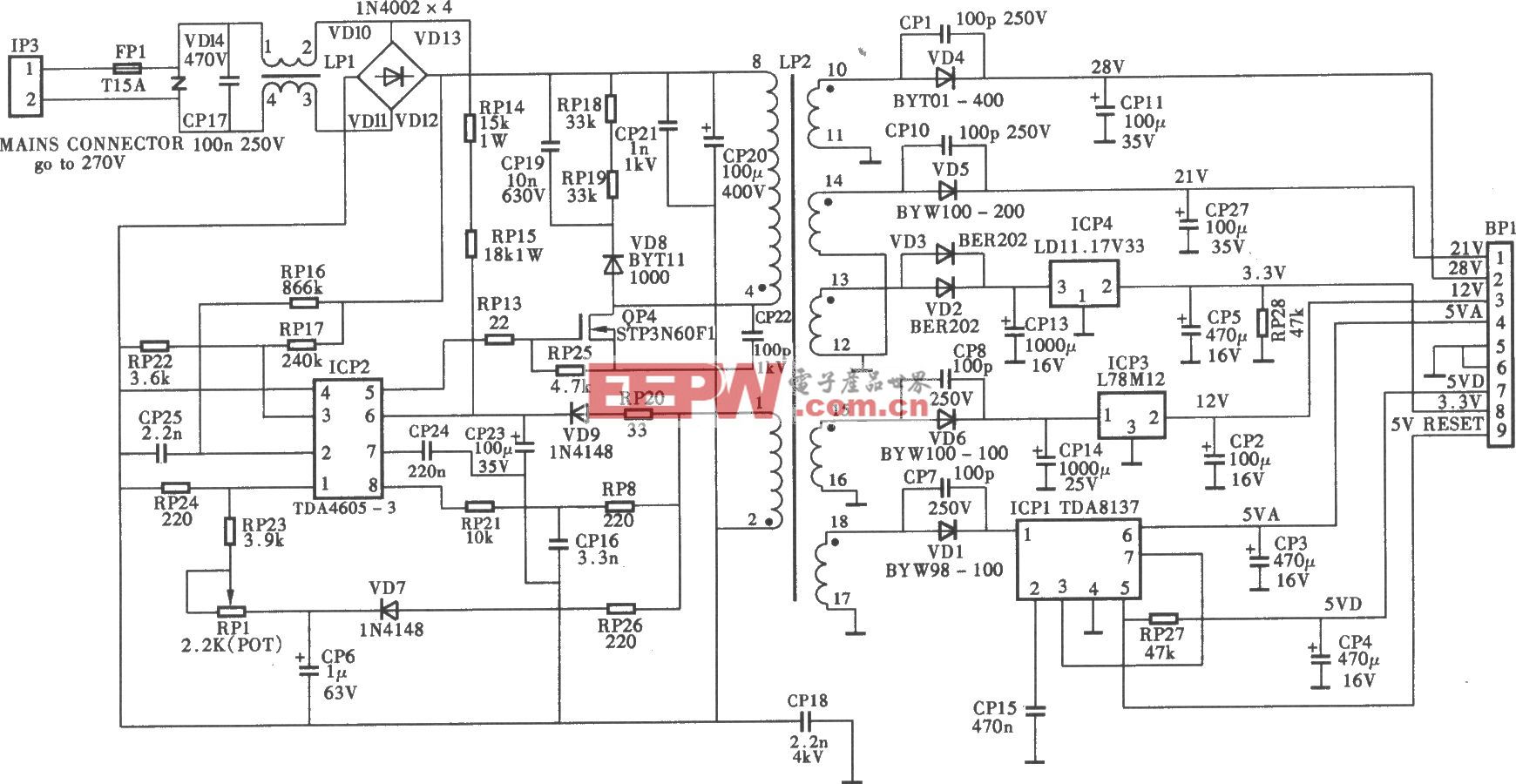

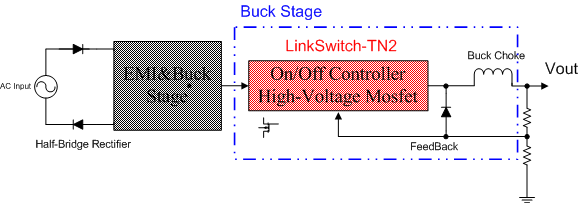

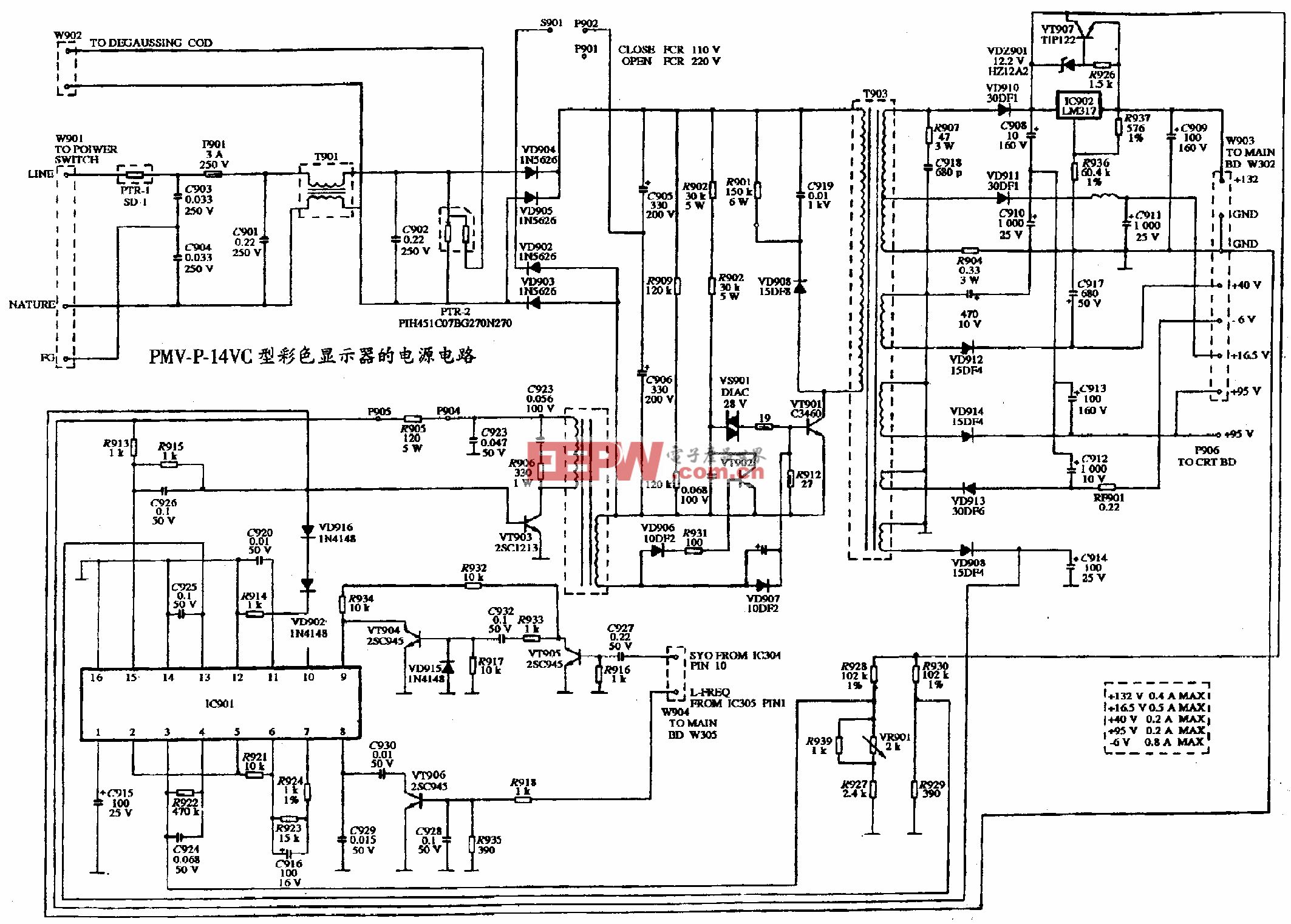

图l是本文采用的电荷泵系统示意图,其中8V和5V电荷泵用于产生一个8V的编程字线电压和5V的擦除源线电压Vpp,-8V和-3.3V电荷泵是一个基于共享技术的电荷泵电路,它可以产生-8V(驱动能力大于10μA)的字线擦除电压和-3.3 V(驱动能力大于l00μA)的位线编程电压Vnp。而-4.8V电荷泵则产生加到选择栅上的-4.8V高压Vnc,用于把-3.3V的编程电压传递到选中的存储单元上,以及用在位线电压转换模块中。钳位电路的作用是对输出高压进行钳位,使得输出高压稳定在所需要的电压值上。而在电路停止工作时,通过泄放通路可以把输出端的电压置为OV。

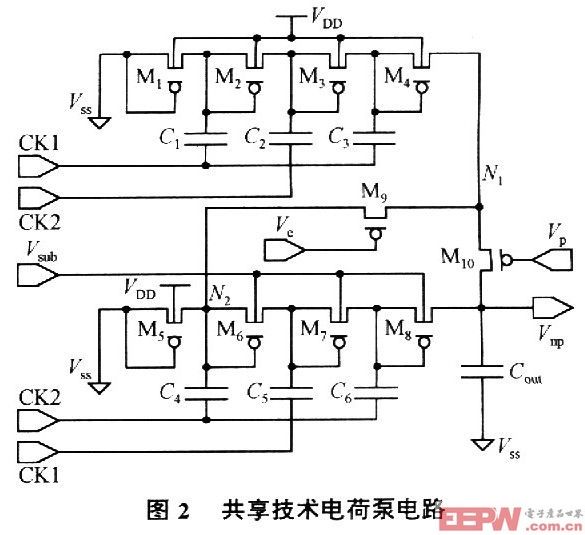

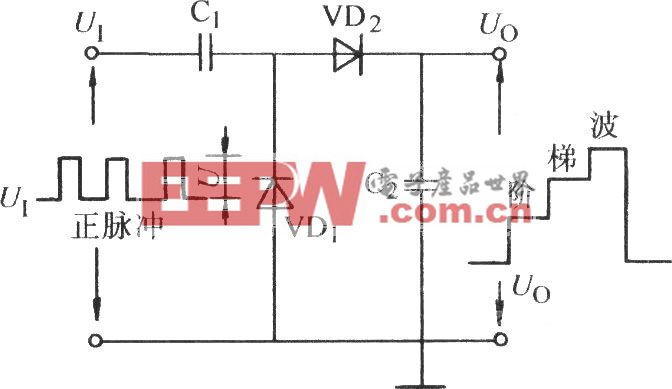

为了降低芯片面积而提出的基于共享技术的负高压电荷泵电路见图2,它可以产生-8V和-3.3V两种负高压,其中Ve和Vp是高压控制信号,Ve可以在Vnp和电源电压VDD之间转换,而Vp可以在-4.8V和VDD之间转换,其中-4.8V来源于-4.8V电荷泵。其输入输出关系如表2所示。当需要产生-3.3V电压时,让Ve等于VDD,而置Vp为 -4.8 V,系统可以看作是两个三级的子电荷泵

(分别由PMOS管M1-M4,耦合电容C1-C3和PMOS管M5-M8,耦合电容C4-C6组成)的并联,在两相非重叠时钟CKl和CK2的驱动下,Vnp输出-3.3V电压,由于连接到C3和C6上的时钟信号分别为CKl和CK2,所以两个子电荷泵在一个时钟周期内将分别对输出端Vnp充电一次。这不仅大大降低了输出端电压的波动性,同时还增加了输出端的驱动能力,满足了多位同时编程时对大驱动电流的需求。如果系统需要-8V的高压,把Vp置为VDD,而把Ve连接到高压输出端Vnp,这样M10将被关断,而刚开始时由于Vnp为0V,所以M9不会导通,电路仍旧处于两个子电荷泵并联工作状态,只是它们的输出端被M10隔开。随着Vnp由0V逐渐变小,它的电压将低于节点N2的电压,M9会逐渐导通,此时系统可以看作是一个六级的电荷泵(由M1-M4和M6-M8以及C1-C6组成),最终系统将产生-8V的高压。这样,和采用两个独立电荷泵分别产生-8V和-3.3V的方法相比,该电荷泵可以节省大约50%的芯片面积。需要注意的是M6-M8的衬底电压由Vsub控制,这主要是为了降低它们的衬偏效应,增加电荷泵的增益。

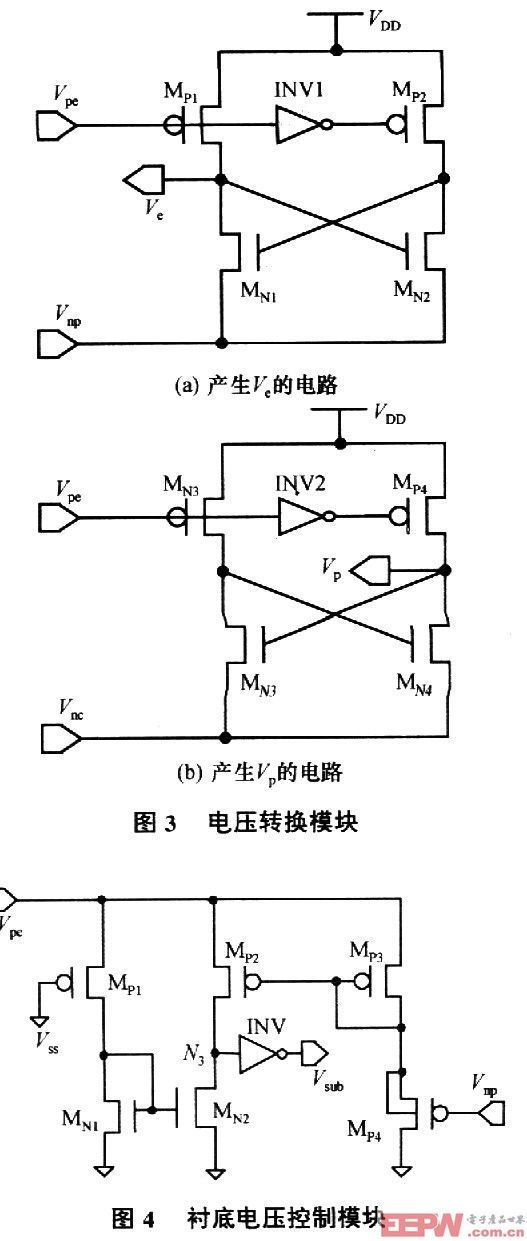

共享技术电荷泵的Ve、Vp时序由图3所示的电压转换模块产生。图3a可以实现Ve在VDD和vnp之间的转换,而图3b实现Vp在VDD和- 4.8V之间的转换。结合图2,其工作模式见表2。当控制信号Vpe为高时,电荷泵产生-8V高压,而当Vpe为低时,电荷泵产生-3.3V高压。

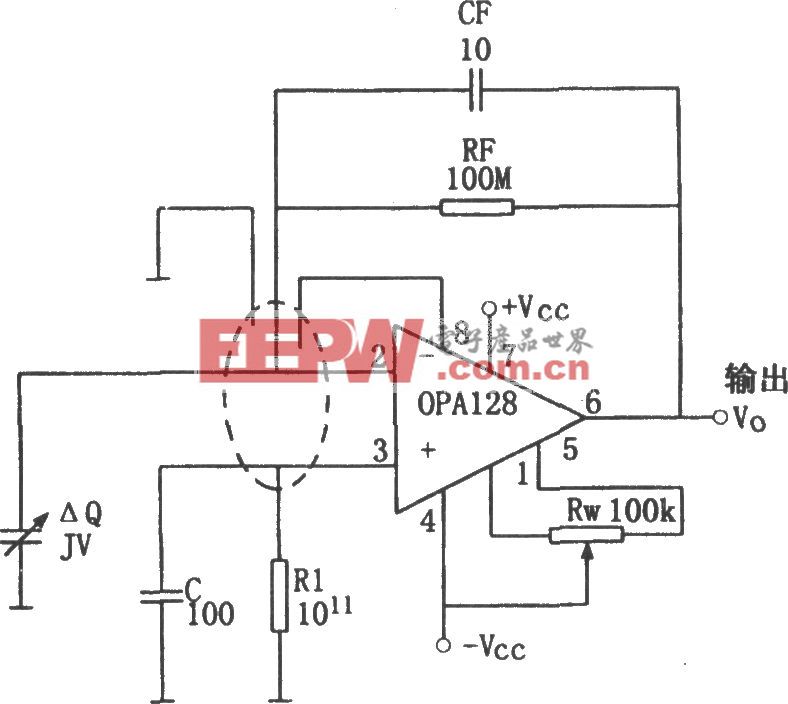

为了降低共享电荷泵中PMOS管的衬偏效应,提高电荷泵的增益,本文采用了一个衬底电压控制模块,见图4所示。其中Vnp连接到-8V和-3.3V电荷泵的输出端,Vpe是控制信号。其中NMOS管Mw1和MN2以及PMOS管Mp2和MP3构成两对电流镜。当Vpe为OV时,该模块将不工作,节点V3等于OV,输出端Vsub的电压等于VDD,并送到图2中的Vsub端,且电荷泵将产生-3.3V高压。当Vpe为高时,该模块开始工作,随着图2中电荷泵的工作,Vnp将由0V逐渐降低,PMOs管MH的导通能力逐渐增大,Mp3和Mp2的栅极电压将逐渐降低,这样Mp2的导通能力逐渐增大,倒相器输入端的电压将由OV逐渐上升,最终倒相器INV开始翻转,Vsub的电压将由初始的VDD变成OV。通过调整图中PMOS和NMOS管的尺寸就可以保证当Vsub变成OV时,图2中PMOS管Mp6-Mp8的p-n结不会正偏。这样就减轻了Mp6-Mp8的衬偏效应,提高了电荷泵的增益。

2 模拟结果

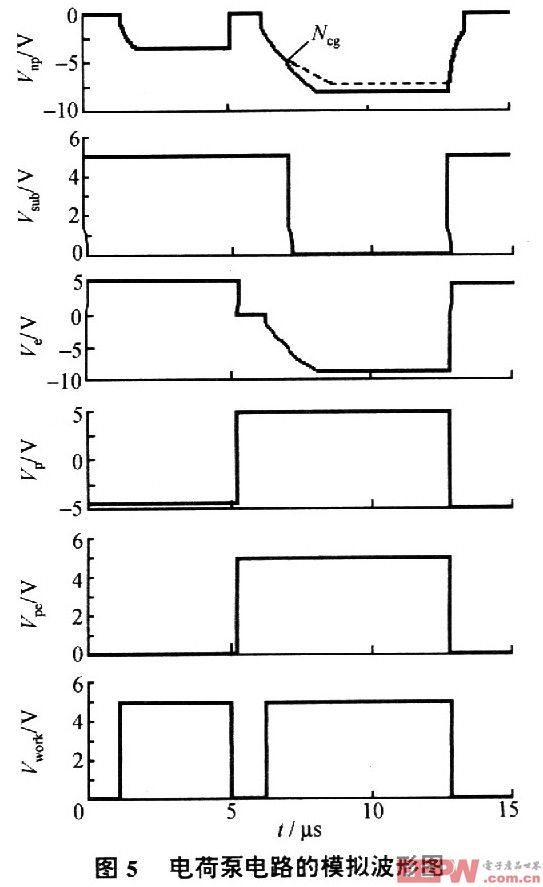

为了验证本文所述电荷泵的性能,采用清华大学微电子所开发的1.4 μm高压工艺参数,用软件HSPICE对其进行了模拟。其中高压NMOS管的阈值电压为0.7 V,高压PMOS管的阈值电压为-0.8V。优化后的耦合电容C1到C6均为12pf,所用的时钟频率为20MHz,电源电压VDD为5.0V。

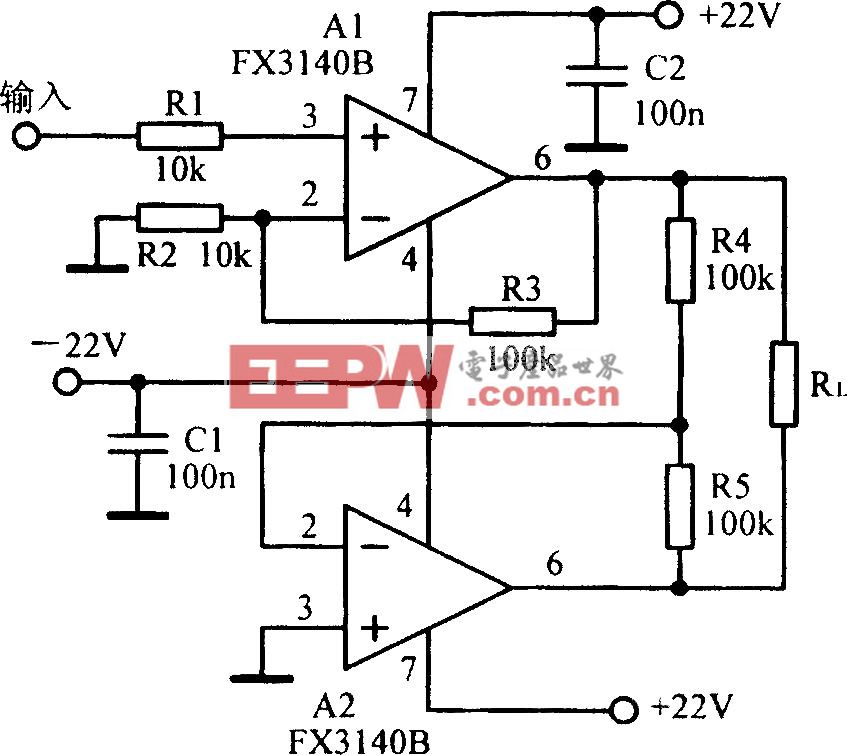

图5是电荷泵电路的模拟波形图。其中Vwkrk是控制信号,当Vwork为高时,输入时钟CKl和CK2,电荷泵电路开始工作。当Vwork为低时,时钟停止输入,电荷泵电路不工作,只是通过泄放通路把输出端Vnp的电荷泄放到地。从图5可以看到,当Vpe为低时,Vp为-4.8V,而Ve等于5.OV,电荷泵电路的输出电压Vnp等于-3.3V。当Vpe为高时,Vp等于5.0V,而Ve和Vnp的电压一致,最终系统输出电压Vnp等于-8V。而且可以看到,当负高压电荷泵工作一段时间,Vnp达到-5V后,Vsub的电压将由5.0V变为0V,这降低了PMOS管Mp6-Mp8的衬偏效应,使得高压输出端Vnp的波形上出现一个拐点Ncg,而且拐点后的电压下降的速度明显加大并最终达到-8V(其中虚线部分是没有采用衬底电压控制模块时Vnp的波形,其电压最终只能下降到-7V),这使得电荷泵的增益提高了大约14%。

3 结 论

本文提出一种基于共享技术的电荷泵电路,通过改变两个子电荷泵的串并连接关系,可以在同一个电路中产生所需的两种负高压,从而节省了大约50%的芯片面积。通过一个衬底电压控制模块对电荷泵中PMOS管的衬底电压进行动态控制,使电荷泵的增益提高了大约14%。该电路特别适用于需要两种以上负高压以完成编程和擦除操作的快闪存储器。

评论