电源模块中DC-DC转换器低电磁干扰设计的折中方法

电源设计中即使是普通的直流到直流开关转换器的设计都会出现一系列问题,尤其在高功率电源设计中更是如此。除功能性考虑以外,工程师必须保证设计的鲁棒性,以符合成本目标要求以及热性能和空间限制,当然同时还要保证设计的进度。另外,出于产品规范和系统性能的考虑,电源产生的电磁干扰(EMI)必须足够低。不过,电源的电磁干扰水平却是设计中最难精确预计的项目。有些人甚至认为这简直是不可能的,设计人员能做的最多就是在设计中进行充分考虑,尤其在布局时。

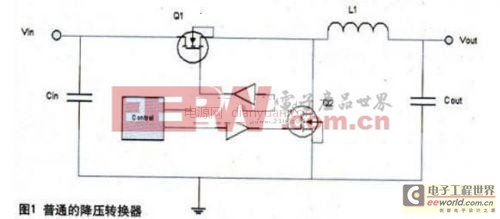

本文引用地址:https://www.eepw.com.cn/article/226996.htm尽管本文所讨论的原理适用于广泛的电源设计,但我们在此只关注直流到直流的转换器,因为它的应用相当广泛,几乎每一位硬件工程师都会接触到与它相关的工作,说不定什么时候就必须设计一个电源转换器。本文中我们将考虑与低电磁干扰设计相关的两种常见的折中方案;热性能、电磁干扰以及与PCB布局和电磁干扰相关的方案尺寸等。文中我们将使用一个简单的降压转换器做例子,如图1所示。

在频域内测量辐射和传导电磁干扰,这就是对已知波形做傅里叶级数展开,本文中我们着重考虑辐射电磁干扰性能。在同步降压转换器中,引起电磁干扰的主要开关波形是由Q1和Q2产生的,也就是每个场效应管在其各自导通周期内从漏极到源极的电流di/dt。图2所示的电流波形(Q和Q2on)不是很规则的梯形,但是我们的操作自由度也就更大,因为导体电流的过渡相对较慢,所以可以应用Henry Ott经典著作《电子系统中的噪声降低技术》中的公式1。我们发现,对于一个类似的波形,其上升和下降时间会直接影响谐波振幅或傅里叶系数(In)。

其中,n是谐波级次,T是周期,I是波形的峰值电流强度,d是占空比,而tr是tr或tf的最小值。

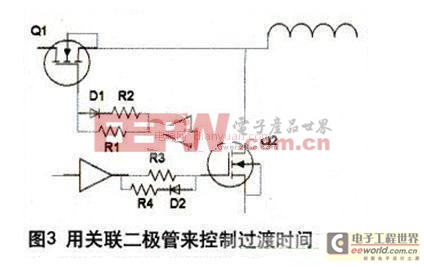

在实际应用中,极有可能会同时遇到奇次和偶次谐波发射。如果只产生奇次谐波,那么波形的占空比必须精确为50%。而实际情况中极少有这样的占空比精度谐波系列的电磁干扰幅度受Q1和Q2的通断影响。在测量漏源电压VDS的上升时间tr和下降时间tf,或流经Q1和Q2的电流上升率di/dt 时,可以很明显看到这一点。这也表示,我们可以很简单地通过减缓Q1或Q2的通断速度来降低电磁干扰水平。事实正是如此,延长开关时间的确对频率高于 f=1/πtr的谐波有很大影响。不过,此时必须在增加散热和降低损耗间进行折中。尽管如此,对这些参数加以控制仍是一个好方法,它有助于在电磁干扰和热性能间取得平衡。具体可以通过增加一个小阻值电阻(通常小于5Ω)实现,该电阻与Q1和Q2的栅极串联即可控制tr和tf,你也可以给栅极电阻串联一个 “关断二极管”来独立控制过渡时间tr或tf(见图3)。这其实是一个迭代过程,甚至连经验最丰富的电源设计人员都使用这种方法。我们的最终目标是通过放慢晶体管的通断速度,使电磁干扰降低至可接受的水平,同时保证其温度足够低以确保稳定性。

评论