系统断电时FPGA数据保护方法

从消费电子设备到工业控制设备,越来越多的系统都在使用FPGA。这些应用通常需要设备在断电时存储一些数据,比如校准信息、用户设置、辨认标签等。如果设备使用了微处理器,则还需要存储微处理器的代码。

对于那些对成本、器件数量以及电路板尺寸不敏感的系统,可采用标准的闪存来存储这些数据。但在许多情况下,成本、器件数量和电路板尺寸等方面的限制导致系统不得不采用双用器件。无论采用单片非易失存储器,还是采用引导用的SRAM器件,FPGA总是具有与它们相联系的非易失存储器。一个显然的问题是,这些非易失存储器是否能在系统关闭时存储数据。

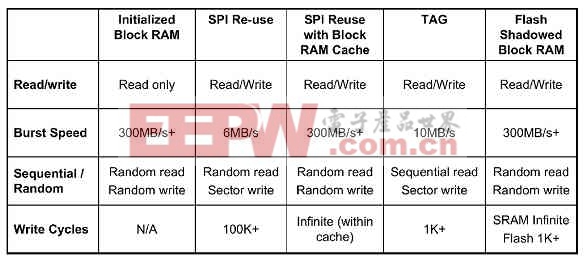

在选择采用哪种方法之前,应考虑应用的要求。这些问题包括: 是否需要进行读/写操作,或者是否接受只读操作;存储的数据有多大;写周期的数量。最后,必须复查与读和写操作相关的特性、时序等。

1.初始化块RAM

大多数FPGA允许其内置的块RAM在引导器件时被初始化。这是一个很好的方法,它提供了较大容量的ROM,可用于存储查找表或程序代码。ROM支持高速随机读取操作,能很容易地对FPGA配置进行再次编程。如果设计需要小容量的ROM,这个方法也不可忽视。

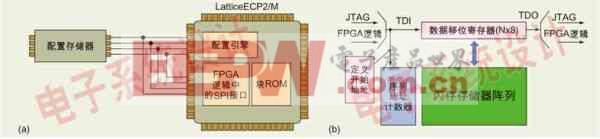

2. SPI重使用

现在所有的SRAM FPGA都允许用SPI存储器来进行配置。因为SPI存储器的附加位很便宜,不会占用电路板的面积,使用SPI存储器的附加空间来存储数据是合理的。在FPGA用其进行配置之后(尽管是各式各样的,设计者使用这个方法前要进行确认),构建SPI接口只需少量逻辑。使用SPI存储器时,要小心避免写到FPGA配置空间中。通过接口逻辑的设计可将其封锁,或者使用在许多SPI Flash存储器中可找到的扇区锁定方法 。

在许多应用中SPI器件允许随机读。用FPGA的存储器块,通过高速缓冲存储当前区技术可实现较高的性能。由于写操作首先要求擦除这个区域,高速缓冲存储方法具有更大的灵活性。利用SPI存储器,擦除/编程周期在正常情况下超过100K。这个规范包括正常的运作期间要若干个上电和断电周期。然而,如果存储器写的次数超过这个数值,则可再次使用存储器高速缓冲方法,防止系统到达SPI的极限。

3.非易失FPGA TAG存储器

现在许多非易失FPGA集成了小的TAG存储器。例如,LatticeXP2提供 0.6~3.4kb的存储器用于此目的。这通常是存储设备设置和校准数据所要求的存储器容量。如图1(b)所示,可以通过JTAG接口或片内逻辑访问LatticeXP2 TAG存储器。在LatticeXP2 FPGA中,对这个存储器的读和写是定序的,支持的写周期超过1K。为简化存储器接口,并使存储器写周期次数最小,可再次利用高速缓冲存储数据技术的优点。TAG存储器与FPGA配置是分开的,因此在这些操作期间,不会写到FPGA的配置中。对集成小的、串行EEPROM而言,片上TAG存储器非常理想。

图1:(a) 用LatticeECP2 FPGA再次使用SPI配置;(b) LatticeXP2 TAG存储器。

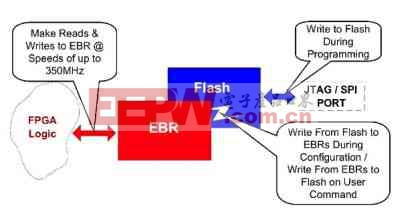

4.闪存影子块RAM

LatticeXP2还提供使用闪存初始化位的功能。配置时,闪存初始化位初始化器件中的每个块RAM。这些存储器可以读和写,就像SRAM一样。当FPGA内必须存储配置数据时,则切换适当的信号使当前的RAM值转入闪存(图2)。这个方法能够对与非易失闪存组合在一起的RAM进行高速读和写 。在LatticeXP2器件中,这个操作支持数千个擦除和写周期。如同TAG存储器,与块RAM在一起的闪存在逻辑上是分开的,这样就能确保FPGA逻辑配置不会意外地被改写。

图2 :LatticeXP2闪存影子SRAM操作示意图。

以上四种方法,每一种方法有其应用优势。如果设计工程师希望采用中等容量的ROM来存储代码或者用作查找表,那么初始化块RAM的方法也许最佳。如果需要存储少量的数据,例如校准信息、当前设置信息或者系统辨别信息,那么TAG存储器方案更方便一些。对于需要再次写入的较大容量的存储器,重使用SPI存储器,或者闪存影子块RAM方法是有用的。当然,无论采用哪种方法,都可以降低电路板的面积和成本。

评论