基于FPGA和SC16C554实现多串口通信的方法

0 引言

随着电子技术的飞跃发展,通用数字信号处理器(DSP)的性能价格比不断提高,数据处理能力不断加强,其应用领域日益增多,在数据实时采集及高速数字信号处理中应用尤其广泛。当DSP独立构成一个处理单元时,往往需要和外设进行数据交换,其通信能力至关重要。在研制机载合成孔径雷达系统时,信号处理机作为系统的核心要与飞控系统、稳定平台、雷达信号源以及导航系统等部分进行数据交换;如何实现其与其它部分之间有效的通信成为系统设计的关键。串口通信因为其简单,可靠仍然是广泛采用的方法之一。

1 串口扩展方案选择

多串口通信常用的实现方案有两种:一种是软件实现,采用软件编程模拟串口,该方法成本低,但编程复杂、开发周期长、可靠性低。另一种是硬件实现,使用多串口单片机或专用串口扩展芯片,该方法虽然成本较高,但是开发比较简单,可靠性高。

目前比较通用的实现方案是采用通用异步通信芯片实现串口扩展,采用FPGA/CPLD实现DSP与异步串口扩展芯片之间的逻辑控制,完全基于DSP接收和发送数据。该方案的缺点是:当数据量较大、多串口同时工作时占用DSP的时间较长,影响DSP的工作效率,且会造成数据丢失。因此本文提出了一种新的实现方法--基于FPGA和通用异步通信芯片实现多串口通信设计。在不进行硬件改动的基础上,通过在FPGA内建立一个缓存机制,实现接收串口芯片的数据,达到一定量时向DSP发送中断读取数据。该设计能极大减少对DSP的占用时间,提高了DSP的工作效率;同时提高了对串口芯片中断请求的响应速度,解决了数据丢失的问题。

2 硬件电路设计

本设计采用通用异步通信芯片SC16C554来实现串口扩展。SC16C554主要特点有:

1.有A、B、C、D四个通道独立收发数据;

2.最高传输速率可达5Mbit/s,具有可编程波特率发生器,便于灵活选择数据收发频率;

3.具有16字节的收发FIFO,且有1、4、8、14字节四个可选择的中断触发深度;

4.可通过编程设置传输数据的格式(数据长度,校验位,停止位);

5.具有可独立控制的发送、接收、线路状态和MODEM状态中断;

6.充分分级的中断系统控制,全面的线路状态报告功能。

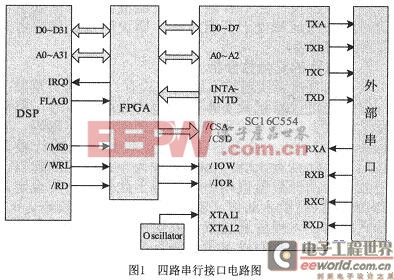

基于FPGA和SC16C554实现多串口通信的基本原理图如图1所示:

3 软件设计及实现

系统实际工作所需波特率分别为9600、38400、115200、153600 。分析计算可得不同波特率发送数据时,连续两个数据之间的时间间隔如表1所示:

由表1可知单个通道连续两个中断产生的最小时间间隔为65μs;因此在65μs的时间内如果可以实现对四个通道分别进行一次读数据操作,即使是四个通道同时来数据也不会发生数据丢失的现象。

3.1 数据的存储设计

即在FPGA内部建立一个缓存机制。设计采用在FPGA内部做一个双端口RAM(DPRAM),用来存储串口数据,DSP通过访问DPRAM得到接收的串口数据。

DPRAM指一个存储模块却包含两个独立的端口,这两个端口共用同一块地址空间,两个端口都可以向这块空间里写数据或从中读取数据。DPRAM的读写数据的模式包括只读、只写、读写三种模式,其中读写模式又包括先写后读、先读后写、只写不读三种模式,我们采用先读后写的模式。

我们将DPRAM的地址空间分为四部分,分别用来存放四个通道的数据。当FPGA收到数据时,我们可以根据置通道标志寄存器CS[2:0]的值来判断该数据来自哪个通道,将其存入对应的地址空间,并将该通道对应地址线加一。当该通道存储数据量达到编程设置的触发深度时,就将DSP中断寄存器dspint置低,向DSP发送中断;同时向DPRAM内一事先定义好的公共存储空间写入通道标志字。当DSP收到中断后,首先访问该公共存储区读取通道标志字,判断该中断是由哪个通道产生的;然后调用相应的接收函数从DPRAM内读取该通道的数据存入指定的地址空间等待处理。

合成孔径雷达相关文章:合成孔径雷达原理

评论