基于FPGA的微型数字存储系统设计方案

1 引言

针对航天测试系统的应用需求,提出一种基于FPGA的微型数字存储系统设计方案。该系统是在传统存储测试系统的基础上,利用可编程逻辑器件FPGA对传统存储测试系统进行单元电路的二次集成,使测试系统体积大幅减小,功耗急剧降低,从而提高系统的抗高过载性能,增加系统灵活性、通用性和可靠性。FPGA不仅完成控制存储及大部分的相关数字逻辑单元电路,而且使得整个存储系统更为简单,布线也更容易。另外,系统FPGA编程就是按照预定功能连接器件内的熔丝,从而使其完成特定逻辑功能的过程,一旦完成编程,FPGA就相当于一片能够完成特定功能的集成电路,因而无需担心程序运行路径出错,这与单片机有本质区别。

2 系统硬件设计

2.1 器件选型

2.1.1 电源

系统中,FPGA工作电压为3.3 V和2.5 V,USB接口器件CY7C68013 工作电压为3.3 V,Flash工作电压为3.3 V,系统需通过电源器件TPS70358将电压转换为3.3 V和2.5 V,为系统各器件提供电源。TPS70358是新一代的集成

2.1.2 现场可编程门阵列(FPGA)XC2S50

该系统采用XC2S50型FPGA控制各个接口,该器件是xilinx公司生产的Sparran II系列高性能现场可编程门阵列(FPGA),具有如下特点:内置标准JTAG接口,支持3.3 V在系统可编程(ISP);3.3 V电源,集成密度为50 000个可用门;引脚到引脚的延时7.5 ns,系统频率高达200 MHz。采用单片FPGA实现逻辑控制功能简化电路设计,提高系统可靠性。且XC2S50系统可编程,只需将一根下载电缆连接到目标板上,就可多次重复编程,方便电路调试。

2.1.3 USB 2.0控制器CY7C68013

CY7C68013是Cypress公司生产的一款USB 2.0控制器,该器件具有运算速度快、功耗小和性价比高等特点。时钟周期高达40 MHz,每执行1条指令需4个时钟周期;其内部集成有USB接口,I2C总线接口等,该系统设计实际数据传输速度高达10 MHz。

2.2 电路设计思路

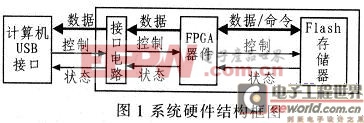

图1为系统硬件结构框图,计算机通过USB接口控制可编程逻辑器件FPGA实现对Flash存储器的块擦除、页编程、读数据等操作。

块擦除操作时,计算机通过USB接口向FPGA发送指令,FPGA接收到指令后对Flash存储器进行块擦除操作,并将状态返回计算机;页编程操作时, FPGA接收计算机并行接口发送的指令,立即对Flash存储器进行页编程操作,先写命令,再写要编程的地址,然后将数据发送到Flash存储器中;读取数据操作时,FPGA首先接收计算机发出的指令,然后对Flash存储器进行读取数据操作,先写命令,再写要读取的地址,然后开始输出数据,并将状态返回计算机并行接口。

评论