以FPGA为桥梁的FIFO设计方案及其应用

引 言

在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据的暂时存储,这就要求大的中间缓存,而专用的高速FIFO芯片价格昂贵且容量受限,大大增加了商业成本,因此在实际应用中寻找FIFO代替器件是很有必要的。

1 器件选择

这里在视频信号处理系统中,将利用FPGA作为桥梁,实现对SDRAM的控制,以达到大量高速存取数据的功能。之所以选取SDRAM,主要是因为在各种随机存取器件中,SDRAM的容量较大,价格较低,且数据突发传输模式大大提高了存取速度,能够满足应用的要求。

FIFO的速度受到两个因素的限制:

(1)SDRAM的最高工作频率。SDRAM的工作频率越高,数据的传输速率就越高;

(2)SDRAM的突发长度。SDRAM的突发长度越长,对数据流的吞吐量就越大,可以从某种程度上提高数据的传输速率。

FIFO的大小由所选SDRAM芯片的容量来决定。该设计以采用MICRON公司的MT48LC4M3282(4 BANK×4M×32 b)为例,存储容量为128 Mb,数据带宽为32位,内部由4个BANK组成,每个BANK有4 096行和256列。

MT48LC4M3282的控制信号有CLK(时钟信号)、CKE(时钟使能)、CS(片选信号)、WE(写使能)、CAS(列有效)、RAS(行有效)、DQM0~DQM3(输入输出使能)。控制信号组成的常用控制命令如表1所示。

2 FIFO系统设计

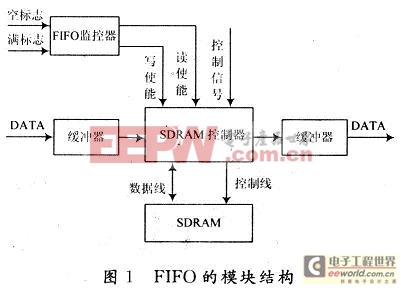

FIFO系统由FGPA和SDRAM两部分组成。其中,FGPA内部包含FIFO监控器、缓冲器、SDRAM控制器三个模块。FIFO监控器的作用是将FIFO的状态转变成状态机的读、写信号。若操作为向SDRAM写数据,则在FIFO已满时,FIFO监控器送出一个信号,以阻止写操作继续向FIFO中写数据而造成溢出;若操作为向SDRAM读数据,则在缓冲器已空时,FIFO监控器送出一个信号,以阻止读操作继续从FIFO中读数据而造成无效数据的读出。FIFO的模块结构如图1所示。

评论