基于FPGA滑动相关法伪码捕获的研究与实现

引言

对于码分多址的扩频通信方式而言,只有当接收端本地伪码与发端伪码处于相同相位状态时,有用的信息才能被解出。因此,扩频序列相位的捕获与跟踪是扩频通信系统的关键,而伪码序列相位的捕获尤为重要。滑动相关法是常用的方法之一。扩频通信系统要求实时性,以及较高的数据处理速度,这正是FPGA的优势。所以在扩频通信系统中,大量应用FPGA芯片作为前级处理芯片。

实现原理

原理分析

接收机端接收到的扩频信号可以表示为:

![]()

其中,P_{r}为接收信号功率,τ_{d}为传输时延,D(t)为信息码, PN(t)为伪码, n(t)为传输过程的加性噪声。扩频接收机要完成的任务就是去掉PN(T-τ_{d}) 伪码项和cos(ω_{0}t+φ) 载波项,从而得到信息数据DZ(t)。

VCO输出I、Q两路信号:

通过同相正交相乘器得到:

利用PN码的相关特性,即相位对齐时,相关结果最大。当载波和码相位都对准时,经过累加清洗(低通滤波)输出为:

![]()

经过平方相加可去掉载波对相关结果的影响,得到相关峰。

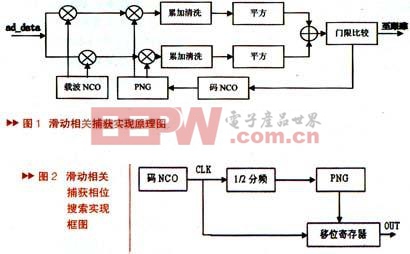

实现框图

在直接序列扩频系统中,伪码的捕获是构成码同步系统的重要结构,也是直扩系统中必不可少的部分。接收机若要把伪码扩展的信号解出,接收方就必须能产生一个与发方一样的伪码序列(保证最大相关值),而且,该本地伪码速率、相位要与接收到的伪码保持一致。对于约定好的收、发方用同一个伪码很容易办到,但是,如果要从解扩相关器得到传送的信息,仅仅保证一样的码型是远远不够的。因为即使相同的伪随机码,当相位差大于一个码片时,它们的相关峰就完全消失。在实际通信中,由于收、发信机时钟的不稳定性,接收、发射时刻的不确定性,信道传输延迟及干扰等因素的影响,收、发伪码序列的相位差是随机的。因此解扩的第一步就是要在接收信号的伪码相位中捕获到一个与本地伪码一致的相位状态。当这种状态出现时相关器就会有一个相关峰值输出,峰值与门限相比,若超出则确定相位已捕捉到,立即停止捕捉动作,转入相位跟踪状态;若小于门限则改变本地码相位,继续进行捕获。系统实现原理如图1所示。

评论