高速流水线浮点加法器的FPGA实现

0 引言

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号处理系统中最重要的部件之一。FPGA是当前数字电路研究开发的一种重要实现形式,它与全定制ASIC电路相比,具有开发周期短、成本低等优点。但多数FPGA不支持浮点运算,这使FPGA在数值计算、数据分析和信号处理等方面受到了限制,由于FPGA中关于浮点数的运算只能自行设计,因此,研究浮点加法运算的FPGA实现方法很有必要。

1 IEEE 754单精度浮点数标准

浮点数可以在更大的动态范围内提供更高的精度,通常,当定点数受其精度和动态范围所限不能胜任时,浮点数标准则能够提供良好的解决方案。

IEEE协会制定的二进制浮点数标准的基本格式是32位宽(单精度)和64位宽(双精度),本文采用单精度格式。图1所示是IEEE754单精度浮点数格式。图中,用于单精度的32位二进制数可分为三个独立的部分,其中第0位到22位构成尾数,第23位到第30位构成指数,第31位是符号位。

实际上,上述格式的单精度浮点数的数值可表示为:

![]()

上式中,当其为正数时,S为0;当其为负数时,S为1;(-1)s表示符号。指数E是ON255的变量,E减127可使指数在2-127到2128变化。尾数采用科学计算法表示:M=1.m22m21m20……m0。m22,m21,…,m0,mi为Mp的各位,设计时应注意尾数中隐含的整数部分1。0是一个特殊的数,0的指数位和尾数位均为0,符号位可以是1,也可以是0。

2电路的流水线结构

一般情况下,结构化设计是电路设计中最重要的设计方法之一,采用结构化设计方法可以将一个复杂的电路分割为独立的功能子模块,然后按一定的原则将各子模块组合成完整的电路,这几乎是电路设计的通用模式。这种设计方法便于设计人员分工合作、实现设计和功能测试,缩短上市时间、升级和二次开发,因而具有其它方法无法比拟的优势。

结构化设计基本上可归结为两种方法:流水线(pipeline)和握手原则。其中握手原则适用于各功能子模块内部运算比较复杂、数据运算时延(latency)不确定的设计。由于数据运算时延不确定,所以,各子模块间的时序配合必须通过握手信号的交互才能完成。握手原则设计的电路一般采用复杂的有限状态机(FSM)作为控制单元,工程设计难度大,故在设计时应慎重使用。流水线法适用于各功能子模块内部运算简单整齐、数据运算时延确定的设计。由于数据运算时延比较确定,各前后级功能子模块不需要任何交互信号就能完成时序配合,故可方便地实现数据的串行流水运算。流水线控制比较简单,一般不需要设计专门的有限状态机,而且工程设计容易,设计时可优先选用。

3 工程的FPGA实现

3.1开发环境和器件选择

本工程开发可在FPGA集成开发环境QuartusII 8.0 spl中完成。OuartusⅡ是世界著名PLD设计生产厂商——Altera公司的综合性PLD开发软件,内嵌综合器和仿真器,并有可与第三方工具协作的灵活接口,可以完成从设计输入到硬件配置的完整PLD设计流程,而且运行速度快,界面统一,功能集中,易学易用。

本设计中的器件选用Stratix IIEP2S15F484C3。Stratix II是Altera公司的高性能FPGA Stratix系列的第二代产品,具有非常高的内核性能,在存储能力、架构效率、低功耗和面市及时等方面均有优势。

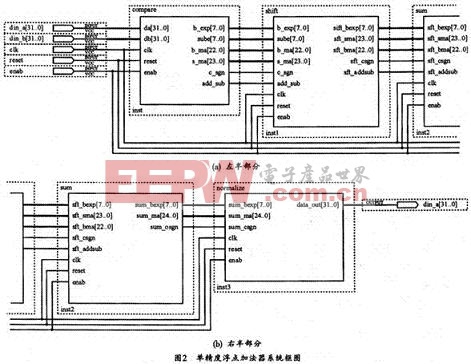

本系统的顶层框图如图2所示。为了显示清楚,图2被分成两个部分显示。本工程采用异步置位的同步电路设计方法,其中clk、reset、enab分别为系统时钟、系统异步置位、系统使能信号。din_a、din_b分别为两个输入的单精度浮点数,data_out则是符合IEEE 754标准的两输入浮点数之和。

评论