RFIC设计所面临的挑战及设计流程详解

无线RFIC设计流程

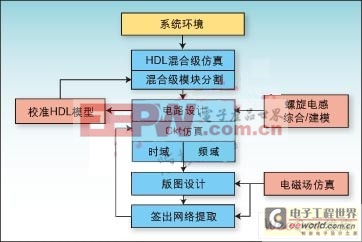

无线RFIC设计流程如图1所示。该流程覆盖了自系统设计到物理实现的全部过程,符合前面谈到的“从两端到中间”的设计方法。

图1:无线RFIC设计流程

1. 使用系统级资源

来自系统设计流程的保证是第一位的,而且是最高的抽象层次,系统级设计描述可作为顶层芯片的可执行测试环境。周边系统的模型可与芯片的高级模型结合起来生成一个可执行的设计规范。系统设计要求可作为最早的设计规范来驱动芯片级的设计要求,并最终成为可复用的测试基准和回归仿真模型。部分系统级的IP资源也可用来确定系统的性能参数(如EVM、BER和PER)。

混合级仿真有助于系统和模块设计工程师之间共享信息。为了保证系统环境和IC环境之间的接口,多模式仿真解决方案必须适合任何语言(包括C/C++、SystemC、SystemVerilog、数字/混合信号/模拟行为级HDL语言以及SPICE),并能为跨多模的电路设计提供不同专用的引擎和算法。

2. 设计规划和仿真策略

一个复杂设计能否成功很大程度上取决于预先规划的彻底性。如果在设计初期就对设计的顶层要求、模块级要求和混合级策略有一个清晰的规划的话,“从两端到中间”的设计方式能够保证所有的模块都能满足主要的设计规范要求,并允许更为灵活的进度安排。因此,全面的仿真策略和建模规划非常关键。在成功实现了高级的可执行规范后,设计过程将深入到设计中某些特定的感兴趣区域,并制定感兴趣区域的验证计划。验证计划会规定测试如何执行,并确定哪些模块在测试中处于晶体管级。工程师要注意在建立和编写模型代码时不要过分复杂化,在开始时只需要简单的模型和必需的模型特性。

正式的规划过程是实现高效、全面验证的前提,有助于在设计初期捕获更多的设计错误并减少设计迭代次数。可以在最初对高级的系统描述采用仿真和测试计划,这样能快速实现调试。经验证有效后,它们会被用于模块的混合级仿真,以减少在设计周期后期出错的风险。

3. 多模式仿真环境

对加入系统级测试基准的RFIC进行HDL建模是自上向下设计过程的开始。这包括全部RF模块,以及所有的模拟部分和/或数字模块。第一步是在一个顶层测试基准中对全芯片进行行为级建模,并进行一些系统测试(如EVM和BER)。这会对IC设计的模块分割、模块功能和理想的性能特性进行验证。这种行为模型可作为混合级仿真的基础,任何模块都可以以晶体管级的形式插入进来并在顶层环境下进行验证。此外,全芯片和系统级的设定可作为一种回归模板(regression template),随着模块逐步成熟而不断用于验证,这也为整个设计过程提供了一种不断演进的设计方法。借助这种方法,在设计初期能够发现大量的问题,并能够保证充足的时间来解决这些问题。同时,不同的模块也能以各自的进度并行开发。

在整个仿真环境中,同一电路有不同的分析视图,其中可能包括行为级视图、版图前晶体管级视图和有关寄生效应的多种视图。随着模块的逐渐成熟,需要增加更多的晶体管级信息以测试RF/模拟接口和RF/数字接口。同时还需要使用混合信号仿真器来处理模拟、数字和RF描述,并将行为级和晶体管级抽象混合起来。为每一个模块或子模块选择合适的视图,管理运行时间和精确度,并在二者之间进行权衡,这可以通过仿真选项来实现,例如将晶体管导入快速Spice仿真器中,或将晶体管保持在全Spice模式下。这种配置对电路和接口的敏感度有很高的依赖性。由于需要重复利用这些配置,对这些配置进行高效的管理显得很重要。这也提供了一种非常有效的机制来建立支持ACD的持续回归验证。

评论