FPGA技术在雷达信号模拟器中的应用

摘 要: 基于FPGA的各种雷达信号产生方法,介绍了在FPGA中实现直接数字频率合成器(DDS)以及提高输出信号质量的方法,编程实现了频率捷变、线性调频以及相位编码等雷达信号的产生。仿真结果表明,该方法能灵活地产生多种雷达信号,且质量较好。

雷达信号模拟器需要模拟简单脉冲调制、重频调制(重频参差、重频抖动和重频滑变)、载频调制(线性/非线性调频、频率捷变)和相位调制(相位编码)等样式的雷达信号[1]。传统的实现方法是采用直接数字合成器DDS实现。通过对DDS相关参数产生对应的雷达中频信号,其优点是产生的信号质量比较好,缺点是系统控制繁琐、模拟的雷达信号参数相对固定、缺乏足够的灵活性,对于非线性调频和相位编码信号很难达到令人满意的效果。

本文基于软件无线电的思想,采用FPGA实现DDS功能,通过控制DDS参数,在1片FPGA中实现了各种雷达信号的模拟。

1 DDS基本原理

DDS由相位累加器、只读存储器(ROM)、数模转换器(DAC)和低通滤波器(LPF)组成。DDS的关键部分是相幅转换部分,根据相幅转换方式的不同,DDS大致可分为两大类:(1)ROM查询表法。ROM中存储有不同相位对应的幅度值,相位累加器输出对应的幅度序列,实现相幅转换;(2)计算法。对相位累加器输出的相位值通过数学计算的方法得到对应的幅度值,实现相幅转换,这里的计算方法有抛物线近似法、CORDIC法等。

对于查询表法,ROM里存储了2N个点(一个周期)。工作过程如下:在时钟脉冲fc的作用下,频率控制字K由累加器累加得到相应的相位码,相位码寻址ROM进行相位/幅度变换输出不同的幅度编码,相当于在ROM里每隔K个点取出一个点,再经过数模转换器DAC得到相应的阶梯波,最后经低平滑滤波器对阶梯波进行平滑,即得到由频率控制字K决定的连续变化的模拟输出波形,输出频率fout为:

式中,K为频率控制字,N为相位寄存器字长。输出频率由频率控制字及相位寄存器字长决定。

理想情况下,由于采样的原因,输出信号频谱存在一些杂散,谱线呈辛格函数形状。DDS输出信号杂散分量较大的主要原因有以下几点:一是相位截断效应;二是存放在ROM中的波形幅度存在量化误差;三是DAC的非理想特性。在DDS中,为了得到高的频率分辨率,相位累加器的字长一般较大,而只读存储器ROM的容量有限,通常位输出中只有高A位用来寻址ROM,从而产生相位截断误差,而DAC和ROM正弦波幅度字长也是有限的,同时,在DAC转换过程中总存在如微分线性误差等误差,这样就产生了量化误差和DAC的非理想特性误差。

2 基于FPGA的雷达信号模拟器

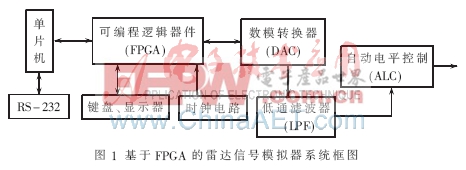

基于FPGA的雷达信号产生器系统框图如图1所示。系统主要由单片机、FPGA、模数转换器、低通滤波器、自动电平控制、RS-232通信接口、时钟电路以及人机接口等部分组成。单片机完成系统控制、人机交互控制以及与上位计算机的信息交换[2]; FPGA实现DDS的模拟以及其他逻辑的产生[3-4];模数转换器将数字信号转换成模拟信号,经低通滤波器滤波后获得良好的波形信号;为了提高信号产生器带负载的能力,自动电平控制部分保证输出信号幅度在接入不同负载时变化不致太大。

系统工作时,单片机将由RS-232接口接收到的或由键盘设置的信号参数写入FPGA,在FPGA中实现的DDS内核根据设置的参数产生相应的数字波形,经D/A转换、低通滤波和电平控制后输出。

评论