在选用FPGA进行设计时降低功耗的方法

如今,各种规范和标准都对系统的整体功耗提出了越来越严格的要求,以至于系统设计师面临越来越艰巨的挑战。

传统意义上,ASIC和CPLD是低功耗竞争中当仁不让的赢家。但是由于相对成本较高,且用户对高端性能和额外逻辑的要求也越来越多,在低功耗应用中使用CPLD正在失去优势。ASIC也面临相同的风险。而例如FPGA这样日益增长的可编程半导体器件正逐步成为备受青睐的解决方案。

开始创建一个新的设计时,物料清单、成本、功耗、电路板尺寸和上市时间都是要认真考虑的因素。在排定初始要求的优先顺序后,在选择FPGA进行系统设计之前,设计师还需要考虑多种因素。

应该

1. 列出你的设计要点。要考虑FPGA在高速、低速或时钟停止情况下的运行时间分别有多长?还要考虑如果器件睡眠时间较长,那么在更高时钟频点的突发模式处理可以达到要求的吞吐量吗?让设计在较低的时钟频率下运行更长的时间是不是更好的选择呢?针对这一过程,FPGA供应商提供了功率分析和预测的辅助工具,但一些工具的分析结果较之实际情况显得过于乐观。

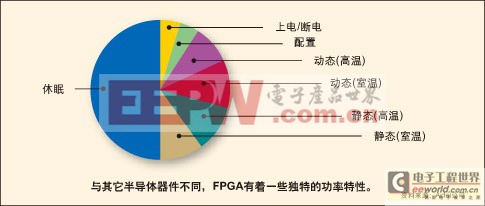

2. 对每一个产品状态都要计算功耗。要计算覆盖整个产品生命周期或预期电池工作时间内的所有状态下的功耗,要考虑到上电、待机、空闲、动态和断电等多种状态。一个应用于具有Wi-Fi通信功能的用户手持设备中的FPGA,其可能只有5%的时间处于工作模式,其它20%的时间处于静态,而75%的时间则处于待机状态。

计算最坏情况下的静态功耗。较新的FPGA技术可能具有超出设计师想像的静态功耗,尤其是在过温条件下。确保考虑了内核、I/O和任何辅助电源。当计算静态功耗时,对每个元件都要应用P=IV计算功耗。

3. 分析可预料的温度和电压变化要覆盖整个产品功耗剖析过程。产品运行期间的热量和电压变化需要计算在内。

4. 估算系统每种工作模式(如短期的高性能工作,长期的低性能工作) 下的电池的工作时间,进而确定最佳的选择。

图:与其它半导体器件不同,FPGA有着一些独特的功率特性。

不应该

1. 忘记使用低功率模式时需要考虑的因素。一些节电模式要求实现时考虑电路板尺寸,因此要求设计应该能够适应这种情况。一些模式不适合被使用,是因为实现过程过于复杂,而且在设备进入或离开某个模式时需要等待一段长到无法容忍的时间。例如,SRAM或SRAM混合FPGA提供的低功率模式要求器件重配置,此时的功耗可上涌至1W。

2. 让用户静态RAM和高I/O电压吸收过多的功率。当使用本地或区域时钟源创建时钟区域时,要使用“enabled”逻辑屏蔽系统中的时钟变化。用户静态RAM可能会吸收过多的功率,因此要选用能少用RAM的技术。I/O也会吸收大量功率,因此建议使用低电压的TTL标准和较低的I/O电压。采用串行低压差分信号片到片数据传输要比片外并行总线节省更多的功率,而它可以采用双倍数据速率寄存器实现。进一步检查元件能否被集成或者功能能否被精简,而较大的FPGA可以容纳微控制器软核,这些都可以节省功耗。

3. 仅依赖于测量得到的功率数据。要根据理论和功率模拟器的数字进行计算,并了解这些数字是如何得来的。这些数字考虑了硅片变化吗?要记住,今天在平台上测得的结果与明天交付的低功率器件的实际表现可能有很大的出入。因此只根据测量数据计算功率时要十分小心。

4. 遗漏额外元件的功耗值。有时用某种FPGA技术实现解决方案可能需要额外的元件。例如,自启动设计可能需要用到存储器,而非易失性FPGA可提供单片实现方案。

评论