基于FPGA的多路数字信号复分接器的设计

1 多信号数字复分接器的设计要求

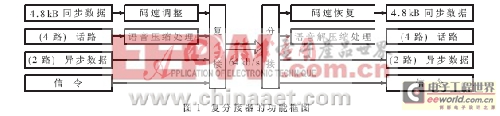

复分接器需要完成对以下信号的复分接:

(1)4路8 kB语音(符合G.729A标准)及线路信令;

(2)1路4.8 kB低速同步数据;

(3)2路最高为2.4 kB的异步数据。

形成速率为64 kb/s的群路码流。功能框图见图1。

2 复分接器的设计与实现

2.1 复分接器的设计

2.1.1 复分接器的帧结构设计

本方案采用时分复用技术,帧结构见表1。

根据表1可以计算出:

每帧的帧长L=1 280 bit

当群路码速率fS=64 kb/s时:

由帧结构设计结果可对信道容量估算如下:

4路话音压缩成23×8×4×50=36.8 kb/s,低速异步数据2路为128×2×50=12.8 kb/s,低速同步数据1路为4.8 kb/s,总开销为54.4 kb/s。

时分复用的分割方式是用时隙实现的,每一支路信号分配一路时隙,帧同步码和其他业务信号、信令信号再分配一个或两个时隙,这种按时隙分配的重复性图案就是帧结构。设计的多路信号复接器,就是按帧结构将各种信息规律性地相互交插汇总成64 kb/s的群路码流。

PCM基群[3]的复接是在时隙信号控制下进行的。以30/32路PCM基群为例,在一个完整的帧周期中,定时系统均匀地产生32个时隙信号,所有时隙信号均和系统时钟同步。在每帧的开始,第一个时隙信号有效,此时在系统时钟作用下,复接器读取第一支路的数据信息(8 bit);接着,第二个时隙信号有效,复接器读取第二支路的数据信息,直至依次读取完所有32个支路信息,如此周而复始进行。这种复接方式以字节为单位进行。

从设计要求可知,复接器要复接的各个支路数据量差别较大,既有8 kB语音信号(该数据由语音压缩电路提供),还有4.8 kB的同步数据及2.4 kB的异步数据。如果按字节方式复接,不仅会造成在不同的时隙中需要复接的有效数据差别很大(如对每一个语音支路、同步数据、异步数据而言,其有效数据分别为184 bit、103 bit、128 bit,而帧对告只需1 bit),而且会浪费较多的系统资源。基于以上分析,本设计采用按位复接。

具体复接过程如下:首先设计一个计数器,该计数器计数速率为64 kb/s,计数范围为0~1 280,与一帧数据的长度正好相同。计数时钟从系统时钟中得到,因而它们是完全同步的。计数器从复位开始计数时,即是每一帧数据的开始。当计数器计数为1时,复接器读取帧的第1位,即帧头的第1位;当计数为2时,复接器读取第2位,即帧头的第2位……,在计数为1 280时,复接器则读取帧的最后一位数据。若按复接支路划分,则有如表2所示的对应关系。

综上所述,可以得出以下结论:复接器应读取的数据位在数值上等于计数器计数值。需要说明的是:CRC采用ITU-T建议的CRC-4方案,其生成多项式为x4+x+1。在计数器值每次变化即复接器每读取一位数据后,立即把该数据发送到群路码流中而不需要进行保存,发送的同时进行CRC校验计算。待需要复接CRC数据时,正好得到其计算结果,不会影响到复接结果。

2.1.2 复分接器的硬件设计

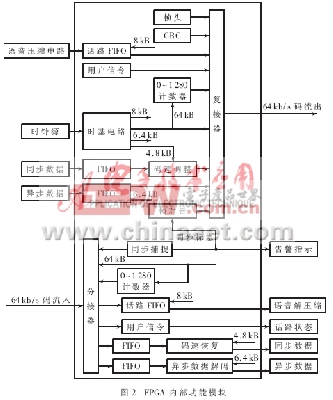

复分接器基于一片FPGA来实现,模块化硬件框图见图2。

2.2 复分接器的设计实现

2.2.1 同步设计

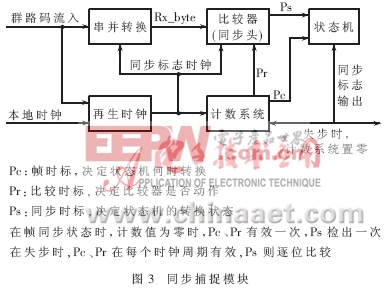

一个时分复用系统必须收、发同步才能正常工作,这个同步包括位同步(时钟同步)和帧同步。位同步是最基本的同步,是实现帧同步的前提。

位同步的基本含义是收、发两端的时钟频率必须同频、同相,这样接收端才能正确接收和判决发送端送来的每一个码元。为此,一般应在传输的群路码流中含有发送端的时钟频率成分。这样,接收端从接收到的码流中可提取出发端时钟频率,通过锁相技术就可做到位同步。

帧同步是为了保证收、发各对应的支路在时间上保持一致,这样接收端就能正确分接出各支路信号。为了建立帧同步,需要在每一帧的固定位置插入具有特定码型的帧同步码。这样,只要接收端能正确识别出这些帧同步码,就能正确辨别出每一帧的首尾,从而能正确区分出发送端送来的各路信号。

常用的帧同步码插入方式有分散插入和集中插入两种方式。分散插入采用把多位同步码分散地插入到信息码流中,最大特点是同步码不占用信息时隙,但同步引入时间长;集中插入则将多位同步码以集中的形式插入到信息码流中,显然,帧同步码需占用信息时隙,但缩短了同步引入时间。

本设计采用帧同步码(1B)集中插入方式。同步捕捉模块框图见图3。

[next]

2.2.2 准同步复接

同步复接是指参与复接的支路数字信号与复接时钟严格同步;准同步复分接则是把标称速率相同、而实际速率略有差异、但均在规定的容差范围内的多路数字信号进行复接分接的技术。

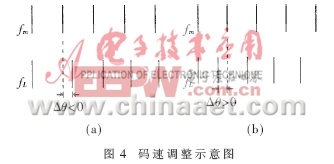

在设计中,由于同步数据时钟和系统时钟不同源,因此,该部分复分接属准同步复分接。码率调整及码速恢复技术是该部分的设计要点,即先把参与复接的各准同步支路码流调整成为同步码流,然后再对这些同步码流进行同步复接;在接收端,则先实施同步分接,得到同步支路码流后,再经过码速恢复装置,把同步支路码流还原成原来的准同步支路码流。码速调整示意图如图4所示。

被复接的码速fL与其标称码速fm之间有三种关系:fLm,fL=fm,fL>fm。当瞬间fL>fm时,采用负码速调整;当瞬间fLm时,采用正码速调整。

在设计的帧结构中,该部分复接后占用的帧长度是固定的,它包含的信息和相应位置如表3。

“插入标志”用来表示采用码速调整的方式,很明显,使用2 bit即可代表三种码速调整方式,在此用6 bit来指示三种码速调整方式,将该6 bit分为3组,对3组数据采用大数判决,可较好解决由于该插入标志误码造成分接时的码流恢复错误。插入码则表示对应的调整码。在分接端,通过读取插入标志即可正确判断和分离出插入码,从而还原成为原来的准同步支路码流。

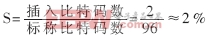

下面对码速调整率进行估算:

其物理意义为:对速率为4.8 kb/s的同步数据,允许的速率变化范围是(4.8-4.8×1 %) kb/s~(4.8+4.8×1 %) kb/s,在此范围内均可完全正确地进行复分接。

2.2.3 语音数据和异步数据的采样

结合图1可知,话音经抽样压缩为8 kb/s,在MCU的控制下,实时写入语音通道的FIFO中,等待参与复接。

异步数据的最高速率限制为2 400 b/s。根据采样定理,FPGA以6.4 kb/s的速率对低速异步数据过采样,使之成为一个同步码流,即可参加复接。

2.2.4 芯片选型

数字复接时,缓存器是必不可少的部件,因为复接过程中,各个支路信号均为连续传输。当复接某一支路信码时,其他支路信码仍在传送,但暂时尚未轮到复接它们,因此需要将这些数据缓存起来,以免丢失。

FPGA既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了ASIC设计的周期长、投资大、灵活性差的缺点。结合性能、成本等要求,设计选用了Xilinx公司的 XC2S300E-6,该FPGA为30万门大规模可编程逻辑器件,基于查找表、触发器结构。查找表可等效为16×1 RAM或移位寄存器,提高逻辑利用率,内置专用双端口BlockRAM,方便了系统开发。

3 设计中需要注意的问题

系统中其他相关设备对群路码流的速率容差要求较为严格,为±50 ppm,因此在选择全局时钟源时应慎重考虑,避免由于时钟源造成的码速抖动和漂移。设计中应多采用同步时序电路来实现各个进程模块的功能,以免电路中产生毛刺。接口数字信号5 V TTL,内部芯片工作电压3.3 V LVTTL,需要进行电平转换。

本设计选用Xilinx公司的ISE6.1作为硬件开发平台,并采用VHDL编程语言。程序已通过了综合实验,并使用ModelSim软件进行了功能仿真和时序仿真,仿真结果正确。在硬件实现与调试过程中,将程序下载到Xilinx公司的SPARTANⅡE系列的XC2S300E-6芯片,经过整体调试,最终实现了对多路数字复分接器的设计。该方法不仅具有通用性、实用性,而且具有灵活性和程序可移植性,相信在很多行业都会得到广泛应用。

评论