单片机驱动CPLD的PWM正弦信号发生器设计

脉宽调制PWM(Pulse Width Modulation)是利用数字输出信号对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。

一、PWM原理

PWM 是一种对模拟信号电平进行数字编码的方法。通过高分辨率计数器的使用,方波的占空比被调制用来对一个具体模拟信号的电平进行编码。PWM 信号仍然是数字的,因为在给定的任何时刻,满幅值的直流供电要么完全有(ON),要么完全无(OFF)。电压或电流源是以一种通(ON) 或断(OFF) 的重复脉冲序列被加到模拟负载上去的。通的时候即是直流供电被加到负载上的时候,断的时候即是供电被断开的时候。

只要带宽足够,任何模拟值都可以使用PWM 进行编码。

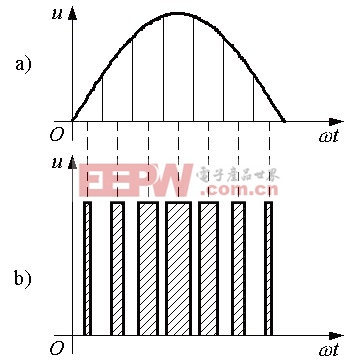

如图1 所示,用一系列等幅不等宽的脉冲来代替一个正弦半波,正弦半波N 等分,看成N 个相连的脉冲序列,宽度相等,但幅值不等;用矩形脉冲代替,等幅,不等宽,中点重合,面积(冲量)相等,宽度按正弦规律变化。

图1 用PWM波代替正弦半波

SPWM 波形——脉冲宽度按正弦规律变化而和正弦波等效的PWM 波形。

二、基于CPLD的PWM方案

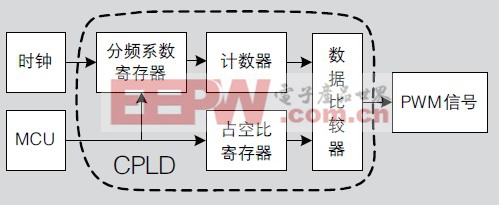

一个PWM 发生器必须包括计数器,数据比较器,另外就是配置PWM 参数的时钟分频寄存器和占空比寄存器,结构框图如图2 所示,这些电路都可以用CPLD 来实现。

图2 PWM控制器结构框图

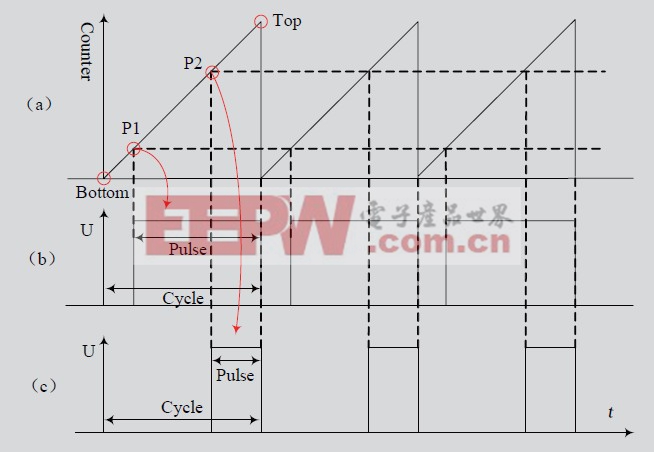

高频时钟信号经分频器驱动计数器,计数器如图3 所示,总是从Bottom 到Top 的循环计数,计数器的输出和占空比寄存器里的数据经数据比较器比较,输出PWM 信号,当计数器输出小于占空比设定值时输出低电平(0),否则输出高电平(1),如图3(b)(c)所示。

图3 PWM信号发生器时序波形图

从图中还可以看出,计数器的周期就是PWM 信号的周期,通过修改占空比寄存器从而实现对输出PWM 信号高低电平比例控制,图3(b)是占空比为P1 的PWM输出,图3(c)是占空比为P2 的PWM 输出,它们周期相同,高低电平的比例不同。

pwm相关文章:pwm原理

负离子发生器相关文章:负离子发生器原理 分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理 脉宽调制相关文章:脉宽调制原理 离子色谱仪相关文章:离子色谱仪原理

评论