基于单片机的压电式贾卡控制系统设计

贾卡经编机贾卡装置自1884年问世以来,已从机械式发展到电磁式和现在的压电式,即Piezo贾卡系统,彻底改变了贾卡装置需要通丝、移位针等繁杂部件的特点,使贾卡经编机提花部分的机构大大简化,速度有了很大提高。此外,与计算机辅助花型设计系统配合,加快了贾卡经编织物的设计,简化了上机工艺,缩短了产品更新周期。Piezo贾卡的成功开发促进了经编机设备的不断发展进步,目前机器速度已经大大提高,提花原理也得到了进一步的发展。

Piezo贾卡导纱针主要由三部分组成:压电陶瓷、导纱针握持端和可替换的贾卡导纱针。Piezo贾卡元件用于控制经编机上贾卡导纱针的左右偏移。它由两片压电陶瓷组成,中间由玻璃纤维层隔离(绝缘)。压电陶瓷具有“逆压电效应”,将其置于外电场将产生几何变形。通过控制贾卡元件两侧交替加上去的正负电压,使电陶瓷变形,进而使导纱针向左或向右偏移。由于压电陶瓷效果像电容一样,使得压电式导纱针能保持在它的偏移位置上。贾卡导纱针左右两面都有定位快,可以保证精确的隔离。

设计贾卡控制系统的主要目的就足要根据经编机的需求,把花型数据准确适时地执行到导纱针,实现经编机的提花。本文根据实际经编机设备的开发需求,选用AVR系列单片机ATmega128为主控芯片,设计了压电式贾卡控制系统,包括控制系统的软、硬件设计,压电陶瓷贾卡装置的驱动电路等。系统将计算机技术和传统的提花工艺结合,较好地解决了传统提花工艺中存在的问题,降低了成本,简化了操作过程,缩短了新产品的开发周期。该系统由于成本低,结构简单,特别适用于实际贾卡经编机设备控制部分的技术改进,具有较好的可靠性与实用性。本系统的设计原理和结构的可靠性与实用性已通过样机试运行得以证实。

1 硬件设计

1.1 系统总体结构

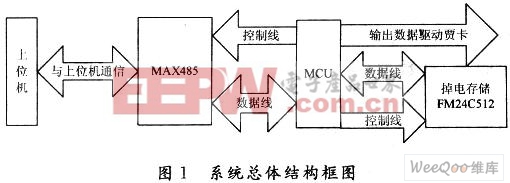

图1所示为系统总体结构框图。

图1中下位机在系统中所完成的主要工作包括:接收上位机的选针花型数据,并存储在下位机的存储器FM24C512中;接收上位机的同步和归零信号,并根据存储器中的选针花型数据驱动贾卡陶瓷导纱针,以实现提花控制。

1.2 单片机控制系统总体设计

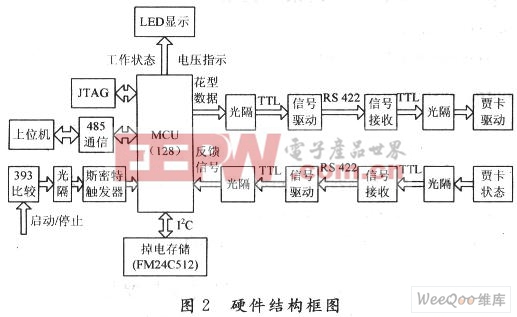

下位机系统硬件结构框图如图2所示。AT-mega128单片机作为系统控制核心,将花型准备系统设计出来的花型数据(花型数据库)通过RS 485连接单片机的串口通信,从上位机把花型数据传送到外部扩展的FM24C512存储器中,实现与上位机的高速多机通讯,并由ATmega128单片机按照花型数据,与机器设备其他部分协调控制(同步、归零等)贾卡经编机所需要的花型,通过贾卡驱动电路驱动贾卡陶瓷导纱针,以实现提花控制。

单片机采用MCU的联机仿真和测试的标准接口(JTAG),可实时在线仿真和调试,方便系统软件的维护和升级。系统工作的启动或停止信号经393比较电路、光电隔离电路和斯密特触发电路处理后安全可靠稳定地到达控制核心,两路信号接ATmega128两路外部中断接口,以保证信号的实时处理。

1.3 硬件各部分设计

1.3.1 MCU控制中心

本经编机贾卡控制系统采用美国ATMEL公司资源丰富的ATmega128产品作为主控芯片进行设计。ATmega128为基于AVR RISC结构的8位低功耗CMOS微处理器,具有快速、灵活、集成度高,加密性强和易实现等诸多优点。ATmega128具有128 KB的系统内可编程FLASH、4 KB的E2PROM、4 KB的SRAM、53个通用I/O口线、32个通用工作寄存器、实时时钟RTC、4个灵活的具有比较模式和PWM功能的定时器/计数器(T/C)、2个USART、面向字节的两线接口TWI、8通道10位ADC、具有片内振荡器的可编程看门狗定时器、SPI串行端口、与IEEE 1149.1规范兼容的JTAG测试接口,以及6种可以通过软件选择的省电模式。由于其先进的指令集以及单周期指令执行时间,ATmega128的数据吞吐率高1 MIPS/MHz,比普通的复杂指令集微处理器高10倍,从而可以缓减系统在功耗和处理速度之间的矛盾。

评论