用电路对采样与保持放大器进行测试

采样与保持放大器对模拟电压执行采样与保持,直到ADC数字化。完善的采样电路一直保持某个电压,直到完成数字化。因此,放大器的输出与它的输入相同。但真实情况中,采样与保持放大器可能会使电压升高或降低,由此产生误差。放大器中的偏移电压会导致静态加法误差。而且会发生一种特定的加法误差,即所谓的电压基底(voltage pedestal),它的起源是在从采样状态向保持状态的过渡中,这一过渡是由于寄生电荷向保持电容器转移引起的。

采样与保持放大器用模拟开关把信号连接到保持电容器。当开关闭合时,电阻很低,因此电容器充电,达到被采样的输入电压。在保持期间,当开关电阻很高时,采样电容器一直保持电压,直到ADC把它数字化。在从低开关电阻向高开关电阻过渡期间,寄生电荷的注入(主要是从开关的栅极向保持电容器注入)不断给电容器充电,直到开关的控制电压达到稳定的逻辑电平。注入的电荷在电容器产生误差电压。在保持期间也许会出现一些额外误差。放大器中的泄漏电流及偏置电流与开关和电容器中的数十皮安泄漏电流结合在一起,导致电容器在保持期间充电或放电。

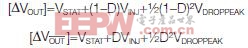

如果应用占空比为D和1–D的逻辑控制信号,你就能测量平均输出压差[∆VOUT ]=[ VOUT – VIN ],如以下方程所示:

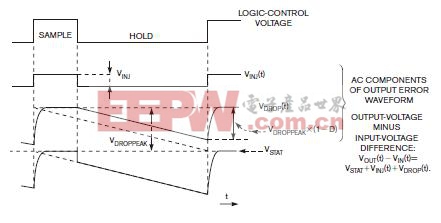

其中∆VOUT和∆V/OUT分别是D和1–D的输出压差,VSTAT是选定的基准输入电压值的稳定输出压差,D是占空比,VINJ是电压基底,VDROPPEAK是压降峰值。图1表明方程中的电压如何随时间变化。如果你应用占空比为25%的互补控制波形,你就能测量采样与保持放大器输出电压的另一个DC分量。最后,当采样开关持续接通时,你可以测量VSTAT电压,它是真正的DC电压。VOUT和V/OUT包含一个波形,它叠加在选定的基准电压值上。因此,你应该用某个阻值(比方说10 kΩ)的串联电阻器测量这些电压的均值。

图1,采样与保持放大器的保持电容器由于泄漏电流、偏置电流以及电压阶跃而出现压降,导致放大器的输出与输入压差。

把电压基底(一个简单的矩形波形)乘以占空比,就得到均值。相比之下,压降波形看起来是一个锯齿。它的均值增加到占空比平方的一半。压降峰值表示样本/HOLD逻辑控制波形的整个周期T结束时的假设压降。

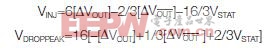

你可用前述方程来求电压基底值和压降峰值。75%占空比是一个很方便的值。下列方程对该占空比有效:

你必须找出逻辑控制信号的最优重复率fREP。在最优重复率上升时,来自输入端的输出压差几乎纯粹是由DC电压偏移加上电压基底导致的:(V/OUT–VSTAT)/(VOUT–VSTAT)≈3。以下方程可求出最优重复率的最大值:fREP≤(0.01/4)×1/(tON–tOFF),其中tON和OFF分别是接通时间和关断时间。该方程确保采样与保持放大器的内部模拟开关的接通时间和关断时间值之差,对精确的25%和75%占空比准确度的影响不会超过1%。

如果你为某种高性能模拟开关(比如Analog Devices公司的ADG1213)求解该方程,你获得的重复率不会超过33 kHz。压降导致的差值在较低的重复率时占优。在此情况下,重复率可以是V/OUT–VSTAT≤1/10×VINMAX时的频率值,其中VINMAX是最大输入电压范围。确定重复率下限的最佳方法是做实验。

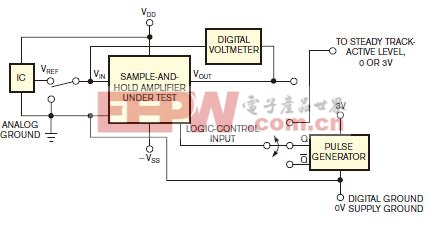

某个受测的采样与保持放大器使用图2中的电路,使用的电源电压为–1V,漏极至漏极电压为5V,并且脉冲发生器中的逻辑电路的电源电压为3.3V。在ADG1213的内部开关的25%、75%和100%占空比数值处的两组测量值控制着使用的0V和2.5V输入电压。你将在1.762 kHz重复率位置测量输出压差(约为–0.0366 mV)和基底电压(约为–0.0333 mV)。进入保持电容器(CH=2 nF)的残留有效电荷注入值QINJ等于CH×VINJ。该值为负,并且不超过–75 fC。以下方程定义了2.5V输入电压范围内的电荷注入差值:ΔQIINJ=QINJ(2.5V)–QINJ(0V),并得出–6.7 fC值。以下方程在重复率为160 Hz时,根据获得的压降峰值确定了残留有效泄漏电流:ILEAK=CH×VDROPPEAK×fREP,其中ILEAK是泄漏电流。0V输入电压时的泄漏电流约为17 pA,2.5V输入电压时的泄漏电流约为–17 pA。

图2,使用数字伏特计来测量采样与保持放大器的输出与输入压差。

评论