可用于高速高精度AD的钟控比较器的设计

在现代通信和信号处理系统中,高性能A/D转换器作为连接模拟和数字世界的重要通道被广泛应用于医学图像、高速数据变换及QAM调制器等重要设计领域。比较器是模数转换器设计的核心单元,其精度、速度、失调电压和回馈噪声等因素直接影响着系统模块的整体性能。传统的预放大锁存比较器通过采用3级或3级以上级联的预放大器结构降低比较器的传输延时和回馈噪声,但这些指标是以较高的功耗和增加芯片面积为代价的。典型的A-B型动态锁存比较器具有高速、低功耗的特点,但该结构存在着较大的回馈噪声和失调电压,限制了比较器精度的提高。综合考虑以上因素,基于TSMC 0.18μm CMOS标准工艺,本文设计了一种可应用于高速高精度A/D转换器的比较器结构,给出了提高比较速度和降低回馈噪声的理论和方法,并基于此进行了电路的设计与优化。

1 比较器电路设计

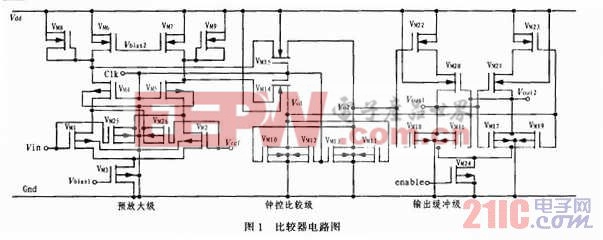

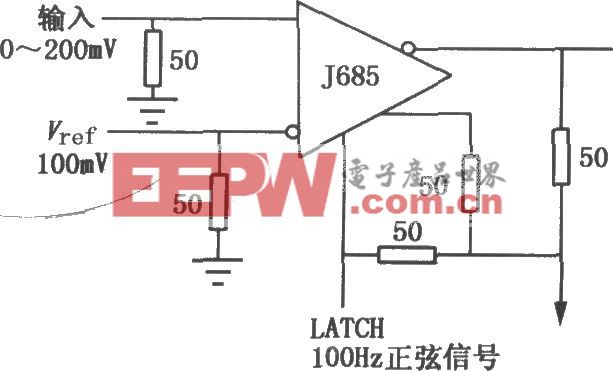

本文设计的高速高精度钟控比较器从功能上可划分为3级,包括预放大级,钟控比较级,输出缓冲级,如图1所示。输入信号通过预放大级电路放大,并由时钟信号控制把放大后的信号传输到钟控比较级进行再生比较,最后利用正反馈结构的输出缓冲级电路将输出电压迅速转化成逻辑电平。

1.1 预放大级

为了满足高速、高精度的要求,预放大器的设计原则是高带宽低增益。单纯的以MOS二极管和电流源为负载的放大器具有有限的增益带宽积,不能同时兼顾速度和精度的要求,使用二极管和电流源负载的混合结构可以满足良好的增益和带宽的折衷。

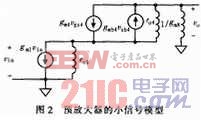

针对图l中预放大级,VM1、VM2构成差分放大管,二极管方式连接的MOS管VM8,VM9为差分对的有源负载,增加PMOS镜像电流源VM6、VM7的目的是使输入晶体管偏置电流的一部分由PMOS电流源提供,这样可以通过减小电流而不是减小宽长比来降低负载管的跨导,进而提高差动增益。VM4、VM5为钟控开关晶体管,当时钟信号clk为高电平时,其与输入差分对构成共源共栅结构,提高电路对输入信号的放大能力;当时钟信号clk为低电平时,其可以有效隔离输入信号与再生节点馈通的回馈噪声,这对保证电路的性能非常重要,预放大电路的小信号模型如图2所示。

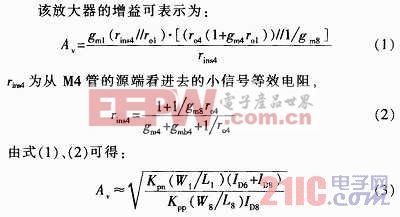

从式(3)可以看出,通过合理调节管子的宽长比和电流源注入的电流值可调节放大器的增益和频率特性。需要注意的是,为同时满足高速比较器对响应时间的要求,设计中在保证增益的同时尽量增加预放大器的带宽。该预放大器的增益、带宽仿真结果如图3所示,增益为18.352 dB,-3 dB带宽为1.122 GHz。

1.2 钟控比较级

钟控比较级响应时间的快慢直接影响着比较器的速度。该部分电路的原理主要是利用预放大器的输出控制比较级输入端电压的变化,即通过预放大级电路将比较器输入差值放大到大于比较级的阈值,避免了比较级的非稳态输出,从而把再生阶段初始时建立的较小的输入电压差在短时间内再生放大,提高了比较器的精度。该钟控比较级(图1)的两个交叉耦合MOS管VM10、VM11的互联实现了用正反馈环路结构提高比较级电路增益的目的。开关晶体管VM4、VM5、VM12、VM13、VM14、VM15共同控制比较级的工作状态,状态转换的快慢影响着比较级的再生速度,MOS开关的响应时间为![]() ,因此可以通过减小晶体管的尺寸来缩短比较级的再生时间,本设计中的开关晶体管均采用该工艺下最小尺寸。

,因此可以通过减小晶体管的尺寸来缩短比较级的再生时间,本设计中的开关晶体管均采用该工艺下最小尺寸。

比较级电路有两种工作模式:复位模式与比较模式。当时钟信号clk为高电平时,VM4、VM5导通使预放大器采集并放大输入信号,VM12、VM13导通和VM14、VM15关断强制将再生节点电压Vo1,Vo2拉到低电平。当时钟信号clk为低电平时,VM4、VM5、VM12、VM13关断,VM14、VM15导通,系统进入比较模式。VM10和VM11栅源电压的不同将导致流过这两个晶体管电流的不同,两再生节点Vo1,Vo2电压上升的快慢就不同,电压上升较快的一端将会抑制另一端再生节点电压的上升,比较级电路正反馈的机制将会使再生节点电压差迅速增加。

1.3 输出缓冲级

目前,A/D转换器中的比较器通常在时钟的跳变沿处进行比较。本文设计的电路是通过在比较级电路后增加输出缓冲级(又称后放大级) ——正反馈的latch结构来实现的,其主要作用是把比较级电路的输出信号转化为逻辑电平(O V或5 V)。

当使能信号enable为低电平时,VM24关断(图1),再生节点电压无法作用于输出缓冲级电路,整个比较系统处于不工作状态。当enable为高电平时,VM24导通,输出缓冲级电路导通。当时钟信号clk为低电平时,VM18和VM19导通,VM16、VM17、VM20、VM21构成了一个首尾相接的放大器,根据比较级再生节点电压的不同将比较器的输出电压VOUT1,VOUT2迅速转化为全摆幅数字电平。当clk为高电平时,VM18和VM19关断,缓冲级电路进入锁存输出信号的状态,保证了输出结果的稳定性。

2 电路的分析和优化

2.1 比较速度

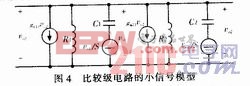

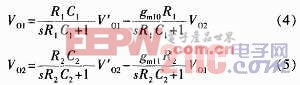

在时钟信号clk为低电平时,钟控比较级电路进入再生阶段,此时该部分电路的小信号模型,如图4所示。

根据小信号模型的节点电流可得到如下公式:

其中,C1和C2是从VM10和VM11的漏极到地的电容,R1和R2是从VM10和VM11的漏极到地的电阻,![]() 为再生节点所加的初始电压。τ为时间常数,假设所有的晶体管相同,则有R1=R2,C1=C2,gm11=gm10=gm,从而τ1=τ2=τ。

为再生节点所加的初始电压。τ为时间常数,假设所有的晶体管相同,则有R1=R2,C1=C2,gm11=gm10=gm,从而τ1=τ2=τ。

用△Vo定义Vo1与Vo2的差值,用△Vi定义![]() 的差值,因此

的差值,因此

需要注意的是:1)在钟控比较级使能之前,再生节点电压变化的速度随△Vi的增加而增大;2)τ的绝对值越小,传输延时越小,比较器工作速度越快。由此可知,通过增加输入跨导、减小输出节点的负载电容和提高初始输入电压差可提高比较器速度。

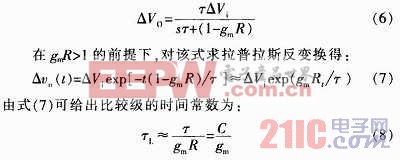

此外,存比较级电路后增加的输出缓冲级电路也能缩短比较器的比较时间。其优点是结合了比较级电路的正指数响应和正反馈latch结构的负指数响应,即比较级电路先经过一时间段将输入信号放大到某一差值Vx,输出缓冲级电路就会迅速将比较器的输出电压转化到逻辑电平。本文设计的比较级电路和输出缓冲级电路的瞬态响应如图5所示。

2.2 回馈噪声

在比较级电路工作阶段,再生节点电压的快速变化通过寄生电容对输入信号引起的干扰称为回馈噪声,其严重影响比较器的精度。在模数转换器中会用到大量的比较器,这些比较器上的回馈噪声将提高ADC的误码率。为了有效地抑制回馈噪声对比较器的影响,本文采用了隔离和互补技术。

在预放大级中增加开关晶体管VM4和VM5,实现了隔离输入信号与再生节点电压的回馈噪声。在比较器从复位阶段转变为比较阶段时,VM 4、VM5关断,切断了预放大器和比较级电路之间的信号通路,使再生节点电压的快速变化无法直接耦合到比较器的输入端,从而降低了回馈噪声。

互补技术的具体实现方法是在预放大级的输入端增加NMOS管VM25、VM26构成的电容,使其与输入晶体管VM1、VM2的栅漏电容CGD构成互补结构。为达到最佳互补效果,CM25,CM26的值应与CGD保持相等,即VM25、VM26的宽度应为VM1、VM2的一半。当输入对管源端电压发生变化时,CM25,CGD-M2和CM26,CGD-M1构成的互补结构使变化的电流相互抵消,从而提高输入电压的稳定性。

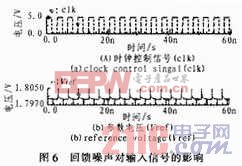

当比较器的时钟频率为300 MHz,输入信号幅度为100 mV时,回馈噪声对比较器基准参考信号产生的尖峰抖动在5 mV以内,如图6所示。与典型的A-B型锁存比较器百毫伏级左右的回馈噪声相比,本文设计的比较器电路结构有较强的抑制回馈噪声的能力。

3 仿真结果

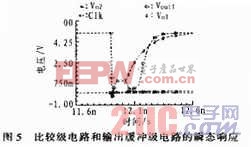

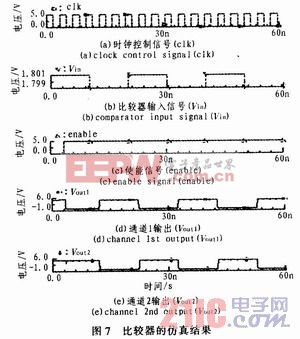

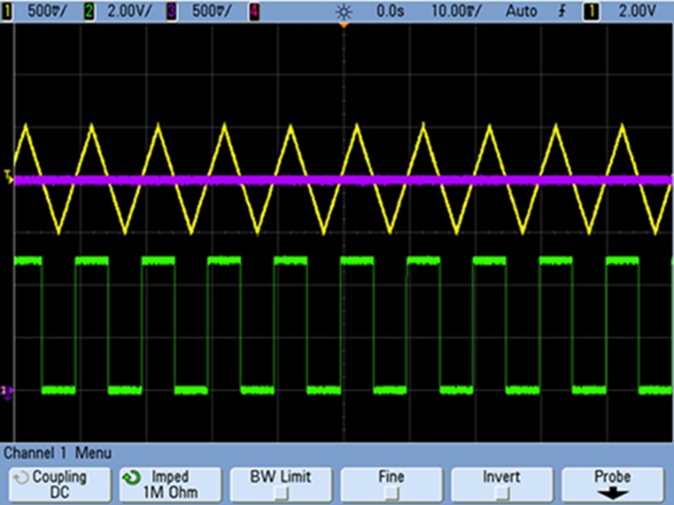

在Cadence软件平台下,用Specte工具对基于TSMC0.18μm CMOS标准工艺模型的比较器电路进行仿真。采用5 V电源电压,300 MHz时钟频率,基准参考电压Vref一直保持为1.8 V,该电路的瞬态响应如图7所示。

第1栏为时钟控制信号clk;第2栏为比较器输入信号Vin,Vin接正负电平为1.801 V和1.799 V的矩形脉冲;第3栏为使能信号enable;第4、5栏为比较器输出节点Vout1和Vout2的波形。图7中曲线表明当enable信号为高电平时,比较器工作并在时钟信号clk下降沿处比较Vin和Vref的大小,在clk上升沿锁存输出结果。当Vin比Vref大1 mV时,输出电压Vout1为低电平,Vout2为高电平,反之输出结果相反。仿真结果符合设计要求,该比较器可达到10位的比较精度。

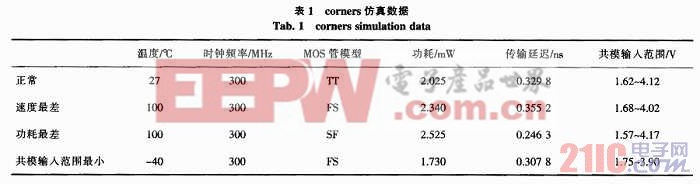

由于工艺及温度变化等因素的影响,实际所得器件参数将产生一定的可变性。为提高产品的成品率及实际性能指标,在27、-40和100℃温度下分别对该电路进行了corners仿真。在不同工艺角下,比较器均可正常工作,其传输延时、功耗和输入共模范围等主要性能参数在一定范围内有所波动,如表1所示。

4 结束语

基于预放大锁存理论,本文设计了一种高速高精度钟控电压比较器。采用预放大级、钟控判断级和输出缓冲级结构实现了高比较速度,获得了较小的可分辨电压。着重分析了改进比较器比较速度和回馈噪声的理论和方法。在TSMC0.18μm CMOS标准工艺下,对可能出现的工艺偏差以及使用温度的变化进行了全面的模拟仿真。仿真结果表明,该钟控比较器在速度、精度、传输延时和回馈噪声等重要性能参数方面有显著的优势,可应用于高速高精度模数转换器与模拟IP核的设计。

比较器相关文章:比较器工作原理

模数转换器相关文章:模数转换器工作原理

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理 绝对值编码器相关文章:绝对值编码器原理

评论