基于FPGA的通用位同步器设计方案(二)

2.2.2 定时误差检测设计

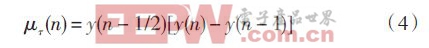

定时误差检测程序采用独立于载波相位偏差的GA-TED算法。该算法每个符号周期只需要两个插值,每个码元周期输出一个误差信号μτ (n) ,即:

其中,y(n) 表示第n 个码元选通时刻的内插值,前后两个内插值的插值代表误差方向;y(n - 1 2) 表示第 n 个和第n - 1 个码元的中间时刻内插值,代表误差大小。

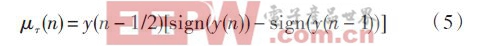

FPGA实现时,为避免乘法运算,采用y(n) 和y(n - 1)的符号来代替实际值[8],即采用式(5)计算误差信息:

根据式(5)进行程序设计,误差的正负方向判断采用case 语句,当y(n) 和y(n - 1) 的符号位分别为“0”和“1”时,y(n - 1 2)的符号位不变;当符号位分别为“1”和“0”时,y(n - 1 2) 的符号位取反;当符号位为“0”“0”或“1”“1”时,令输出的μτ (n) = 0.TED程序在1 Ti 的时钟控制下进行运算,最终得到29位误差数据,并以1 T 的速率即码元速率输出至环路滤波器电路。

2.2.3 环路滤波器设计

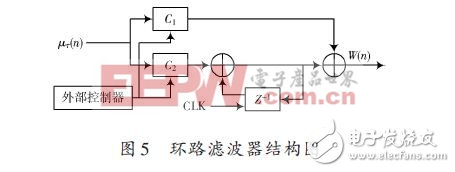

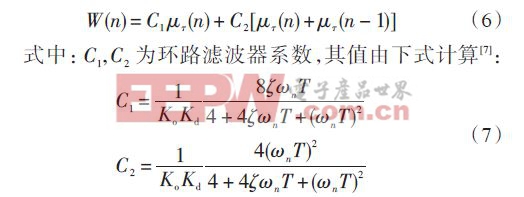

本文对Gardner算法中的环路滤波器进行了改进,根据通用位同步器的要求,采用二阶数字滤波器,并且开放滤波器参数(C1,C2 ) 和使能(c_en)端口,当码元速率变化时,通过外部控制器来改变参数,实现滤波器的通用性。滤波器结构如图5所示。

从图5可以看到,滤波器的输出为:

式中:Ko Kd 为环路增益;ζ 为阻尼系数,取ζ =0.707;T 为采样时间间隔,即相位调整间隔;ωn 为无阻尼振荡频率。

为减少资源占用,环路滤波器中的乘法运算均采用移位方式实现,处理后的误差信息送给内部控制器。

2.2.4 内部控制器设计

内部控制器根据定时误差信息,调整插值频率1 Ti和误差间隔μk ,并输出位同步脉冲BS,它包含NCO(Numerically Controlled Oscillator)和误差间隔计算两部分。该程序提供接口(频率字fw 和使能端fw_en),外部控制器可以通过该接口输入参数。

本设计中NCO 采用与文献[10]类似的DDS(DirectDigital Synthesis)结构,其频率控制字Fw 可由外部控制器设置,其结构如图6所示。

评论