高速大容量存储系统设计

0 引言

本文引用地址:https://www.eepw.com.cn/article/202559.htm在测量技术中,高速数字摄像机所拍摄到的大量数字图像需要高速、大容量的图像存储设备来实时快速地存储。用传统的磁带方式来记录数据,其效率和安全性不高;静态存储器读写方便,但是存储的数据会因断电而丢失,所以不利于数据的长时间保存。而近几年问世的闪存以其存储容量大、体积小、可靠性高等优点,逐步向存储系统进军。

1 设计原理

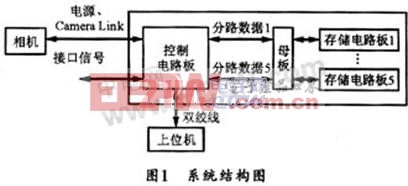

设计中相机输出LVDS串行数据通过接收电平转换和串并转换后得到10路×8 bit的并行数据流,其数据流速率最大为66 MHz。之后根据相机MC1311的性能指标可计算出Camera Link高速接口与数据存储系统的存储容量要求与存储速度要求,即:单帧数据量为1280×1024×8 bit;每秒最大数据量为500×1280×1024×8 bit;Camera Link高速接口单路数据速率为65.536 MByte,如果需要连续存储60秒的视频数据,则需要40 G Byte存储器容量。100 GByte的存储容量最多大约可存储2.5分钟视频数据。图1为系统结构图。

2 核心器件选择

设计中的存储芯片采用SAMSUNG公司的NAND FLASH芯片K9 K8G08UOI,它的外部接口最高速度为40 MHz,接口宽度8位。每个芯片有8192块,每块有64页,每页大小为(2K+64)Bytes,其中64 Bytes为空闲区,存储容量为8Gbit。它以页为单位进行读写,以块为单位进行擦除。控制核心FPGA采用ALTERA公司STRATIXⅡ系列的EP2S30F672I4,它有着丰富的触发器和LUT,非常适合复杂时序逻辑的设计,具有1.3Mbit的内置存储RAM,可以缓存一定量的数据。

3 系统设计

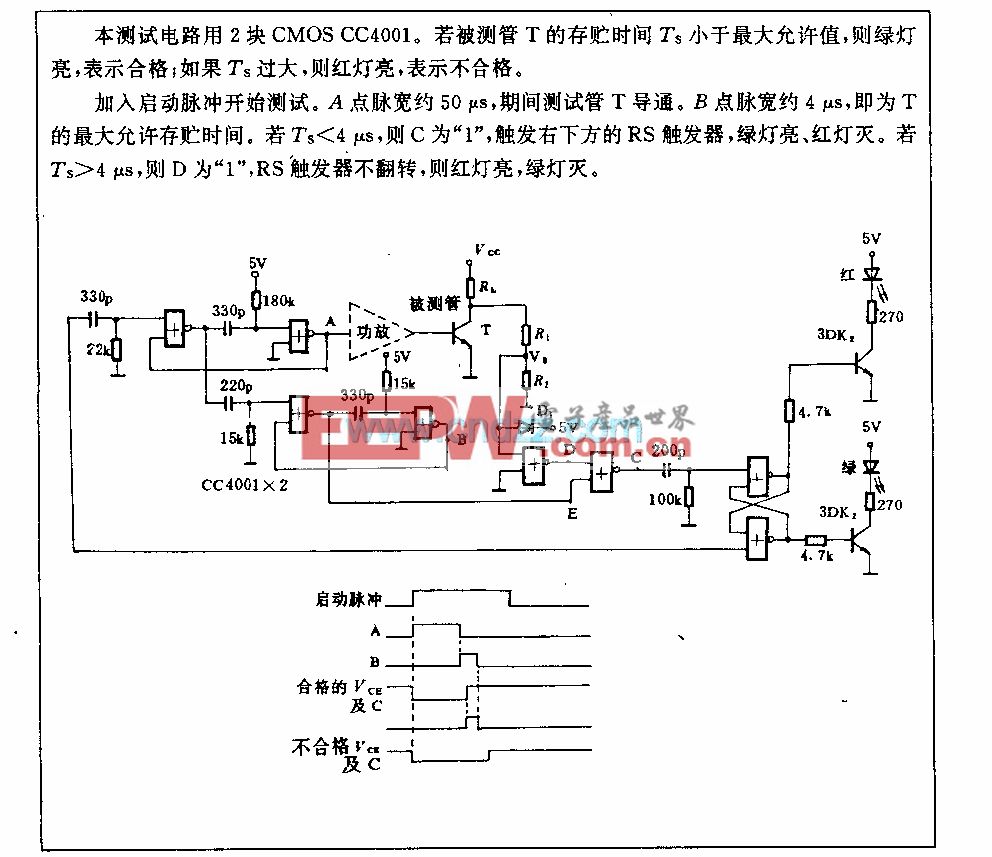

NAND Flash的数据存储采用页编程方式写入,K9K8G08UOI的页写入时序如图2所示。

评论