两家欧洲大学研发300Gb/s 150GSa/s 7 位 DAC

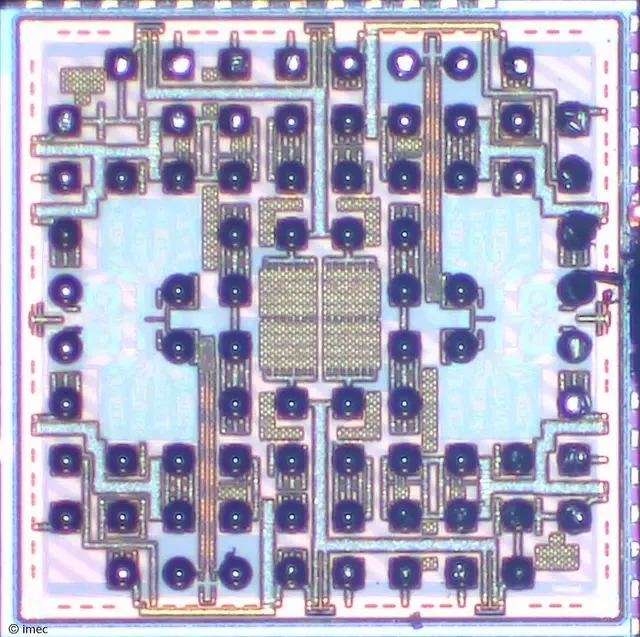

根特大学和比利时安特卫普大学的 imec 研究小组 IDLab 开发了一种采用 5nm FinFET CMOS 工艺制造的 7 位 150 GSa/s DAC,使用 PAM-4 调制可实现高达 300 Gb/s 的数据速率。

本文引用地址:https://www.eepw.com.cn/article/202506/471654.htmDAC 旨在满足对更快数据中心链路日益增长的需求,将速度和能效相结合,为有线数据转换设定了新标准。

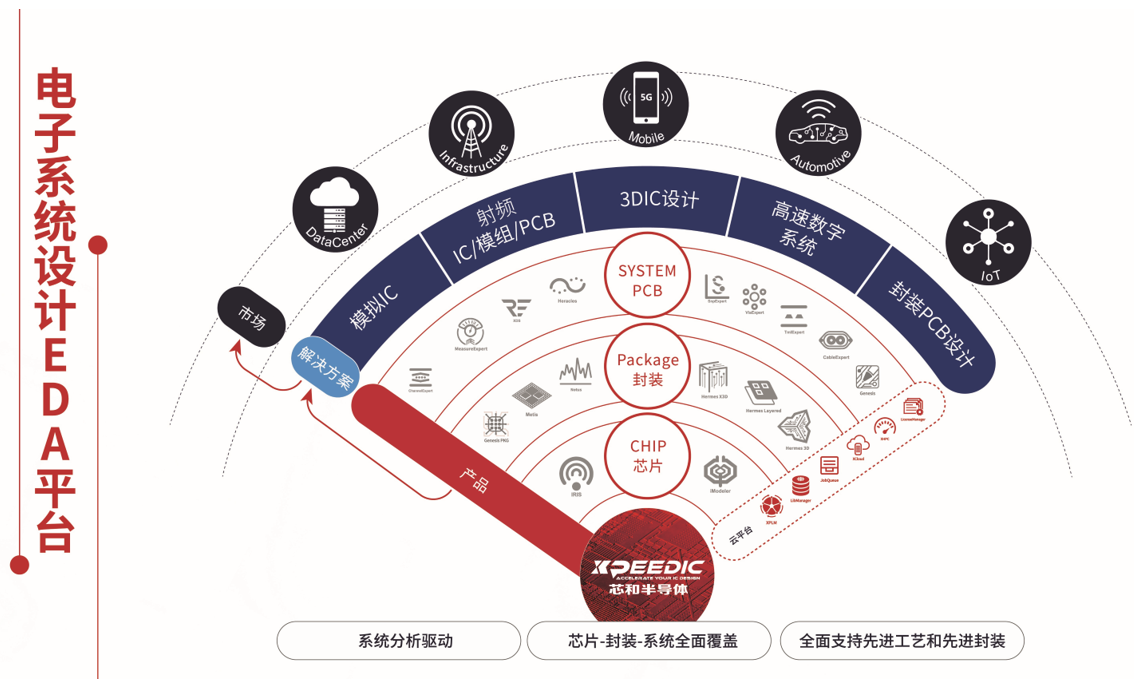

随着机器学习和 AI 等数据密集型应用程序变得越来越普遍,数据中心对更高数据传输速率的需求持续激增。

因此,超高速 ADC 和 DAC 对于确保下一代有线系统中的数据流至关重要。传统架构经常不足,导致信号衰减和功率效率低下。

与此同时,随着部署在大型数据中心基础设施内的互连数量的增长速度超过计算量的增长速度,电源效率变得越来越重要。

PAM-4 已成为数据中心的首选调制方案,无需更多带宽即可实现更快的数据传输。

这款 7 位 DAC 专为下一代数据中心链路而设计,目标是数据速率超过 200 Gb/s,并最终达到每通道 400 Gb/s。为了有效地管理这些速度,在 5nm FinFET 等高级 CMOS 节点中实施了必要的信号处理。因此,DAC 也必须在同一技术节点内实现。在缩放 CMOS 节点中集成如此复杂的架构,利用了 imec 在先进集成电路设计方面的独特专业知识,“imec 高速收发器项目经理 Peter Ossieur 说。

为了优化电源效率,imec 对 DAC 架构进行了创新,将单晶电池的数量从 127 个大幅减少到 34 个。这最大限度地减少了开关活动,有效地降低了功耗(在 0.9V 和 0.96V 电源下降至 621 mW),而不会影响速度。这种减少还减少了寄生效应,从而在更高的数据速率下实现更精确的信号转换。

Ossieur 补充道:“展望未来,该团队旨在通过瞄准基于 3nm CMOS 技术的下一代 ADC 和 DAC,满足对更快数据链路日益增长的需求。重点是将采样率提高一倍,达到 300GSa/s,并将带宽推高到 100GHz 以上。为了实现这样的速度,imec 将利用其在模拟设计方面的专业知识,现在还将解决针对飞秒级精度的超低抖动时钟生成电路的设计问题。

评论