3D封装香了,解决设计痛点需要强大利器

我国芯片业迎来黄金发展期,业界在期盼弯道超车、换道超车,但这需要技术和技巧。2.5D、3D封装是日趋流行的方法,但也随之提升了设计难度。如何破解这个设计上的痛点?

本文引用地址:https://www.eepw.com.cn/article/202111/429335.htm近日,Cadence发布了全新的设计工具——Integrity 3D-IC,值此机会,电子产品世界记者采访了Cadence数字与签核事业部产品工程资深群总监刘淼先生。

1 为何要进入到2.5D、3D封装?

摩尔定律曾经是半导体业的金科玉律,指当价格不变时,集成电路上可以容纳的元器件的数目,大约每隔18~24个月就会增加1倍,性能也将提升1倍。

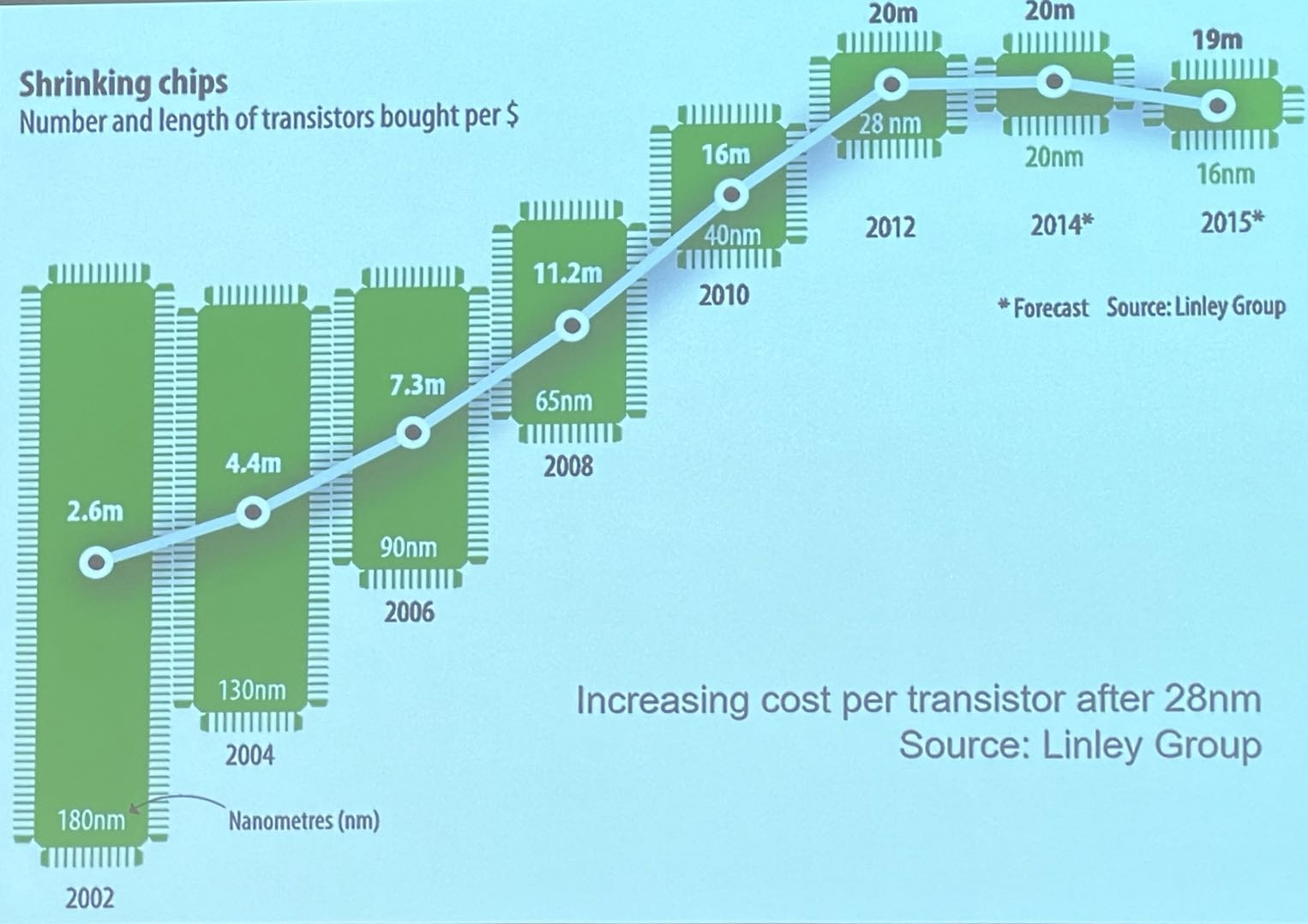

实际上,摩尔定律是经济学定律,近年已经放缓,快走到尽头。因为在经济学上它的成本反而增加了。下图显示了1美元做出来的晶体管加起来的长度,在2002年的工艺是180 nm,1美元做出来的所有晶体管加起来长度是2.6 m;到了2004年是130 nm,做到4.4 m;2006年是90 nm,增长到7.3 m。可见长度一直在增长,到2012年28 nm时,晶体管总长度是20 m。但是,2014年20 nm的时候还是20 m——已经进入了停滞的阶段,再往后会看到这个曲线往下降,原因是到了先进工艺FinFET,成本增加了,例如制造的mask(光罩)层数多了。

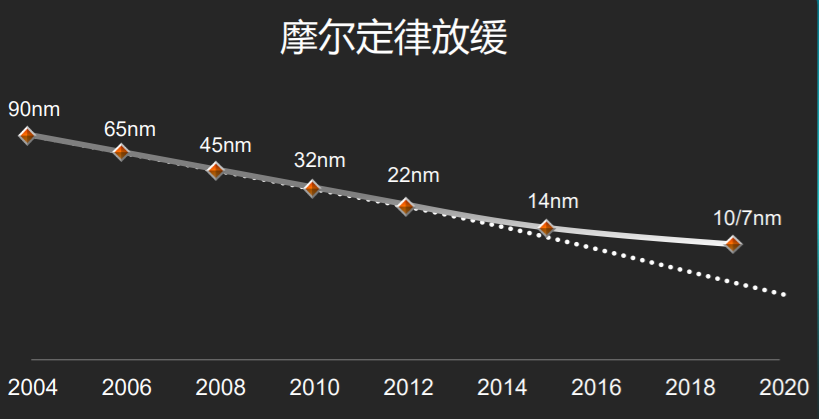

AMD总裁兼首席执行官Lisa Su在一次主题演讲中也认为,自2012年开始摩尔定律放缓了,而且偏差越来越大。

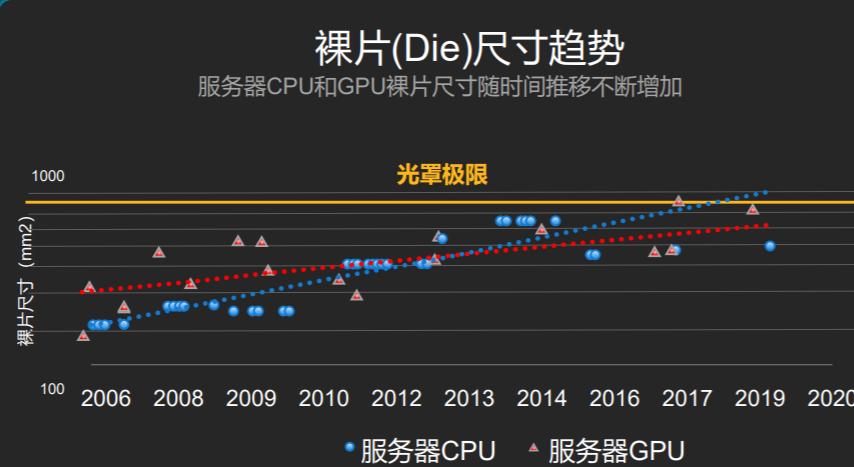

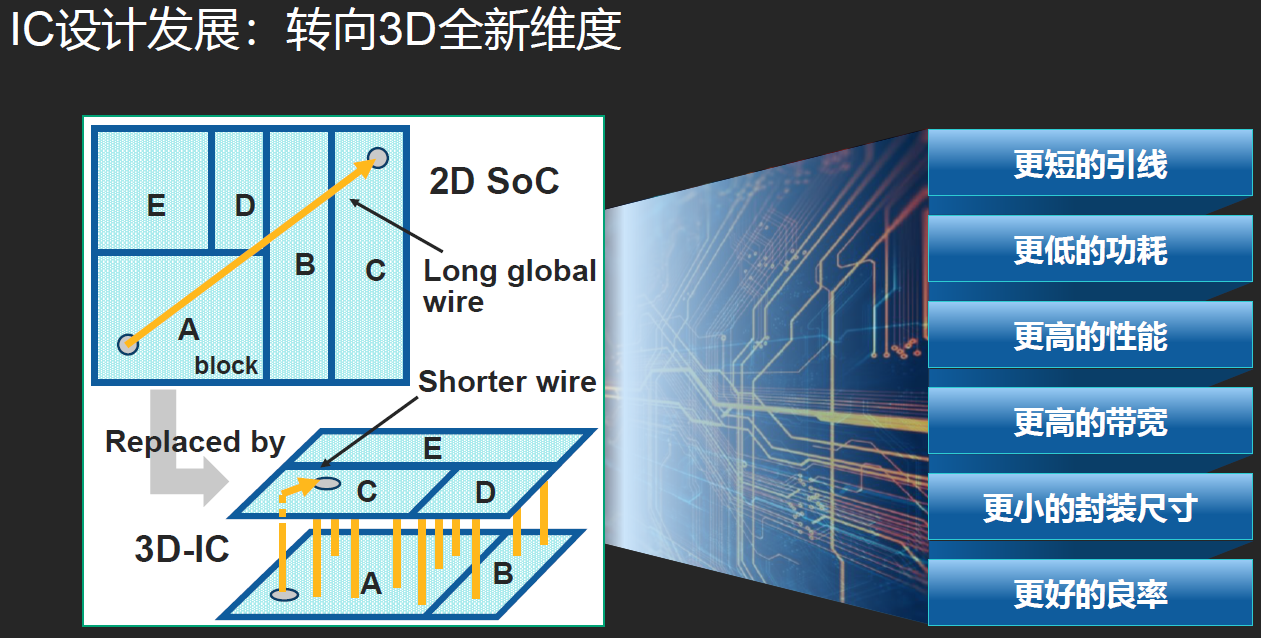

这时就带来了不可调和的矛盾:芯片的功能越来越多,但晶体管无法往下缩小线宽。这导致Die(裸片)尺寸越来越大,因此要从另一维度——2.5D/3D封装开发。

所以为了让摩尔定律继续往下走,需要从2个不同的维度出发。

①More Moore,即深度摩尔,从材料、结构和工艺并举,以前是铝介质,后面是铜,再后面是high-k,之后是FinFET,再往下到了3 nm,还有新的工艺GA(环绕型),2 nm……。

但是仅靠这个维度是不足以支撑摩尔定律继续往下走的,因为看不到显著的成本降低。所以还需要另外一个维度——More than Moore(后摩尔时代)。

② More than Moore是从系统角度出发,走堆叠技术,使得在单位面积上密度会增加。

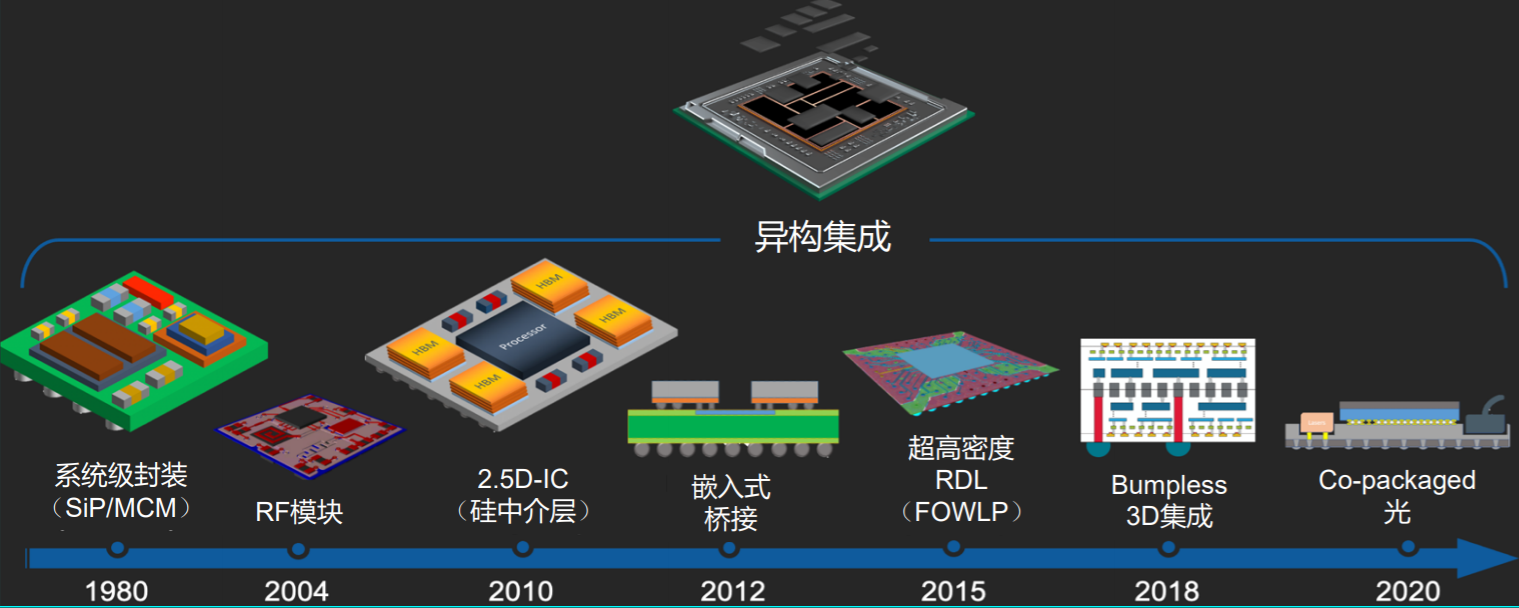

2 堆叠封装的演进

从1980年就出现了由多个芯片堆叠的系统级封装(SiP)/MCM,此后封装技术一直在演进。从Cadence的封装发展史可见,Cadence在2004年做出了RF模块,2010年开始研发2.5D-IC技术,2012年出现了嵌入式桥接,现在用得最多的是FOWLP,还有Bumpless 3D集成,以及最近和很先进的用户做Co-packaged光——把光和硅堆叠起来。

封装的焊球起初是很大的,在1 mm2的间距里间隔小于1个,所以导致这个芯片的bandwidth(带宽)不会太大,通过焊球的速度也不会很快。

后来,封装和芯片之间有新的C4 Bump,间距就会小很多,在1 mm2下可能有16个焊球,所以容量会变得更大。

2.5D技术又往前进了一大步:2.5D下面就是中间层,中间层和芯片之间通过Micro Bump连接,之间的间距会更小,变成50μm左右。间距小了以后,连线就会多很多,使芯片的容量和速度都比以前大很多,这就是为什么一些领先的代工厂在做或想做2.5D先进封装的原因。

在这个基础上出现了更先进的技术:在两个裸片之间做连接,例如Wafer -Bonding,间距有可能从2位数变成了1位数,在1 mm2上就会大于1万个点,速度和容量会大很多。

因此,从2D走向3D的优势是: ①连线更短。②有更低的功耗,挑战是从90 nm到45 nm、28 nm、7 nm……,线上的延迟会越来越多,功耗也会越来越大。③更高的性能。线上延迟减少了以后,芯片就会运行得更快。④更高的带宽。例如很多客户喜欢把芯片跟HBM放在一起,相比DDR4、DDR5或DDR6,HBM的优势之一是带宽高,但是速度稍逊。⑤封装的尺寸会小很多。目前封装也是一个痛点,很多客户拿不到产能,不一定是晶圆厂的产能拿不到,而是封装厂的产能拿不到,因为大基板是很难做。⑥更好的良率,在晶圆厂流片时,良率和面积是呈指数关系的,往往面积越大,良率越低。

3 3D封装的设计挑战是什么?

刘淼曾陪客户的工程师查看一个大的yield(良率)问题,因为客户的芯片很大,有20多个裸片,但良率没有规律,出现坏点的地方是随机的。因此这种情况下,只能尽量把芯片面积做小。所以3D堆叠把以前很大的芯片分成两三个小的,良率会上升,制造成本下降。但是3D的设计成本要增加,因为比以前复杂很多。

综合起来,3D封装主要有以下2个痛点。

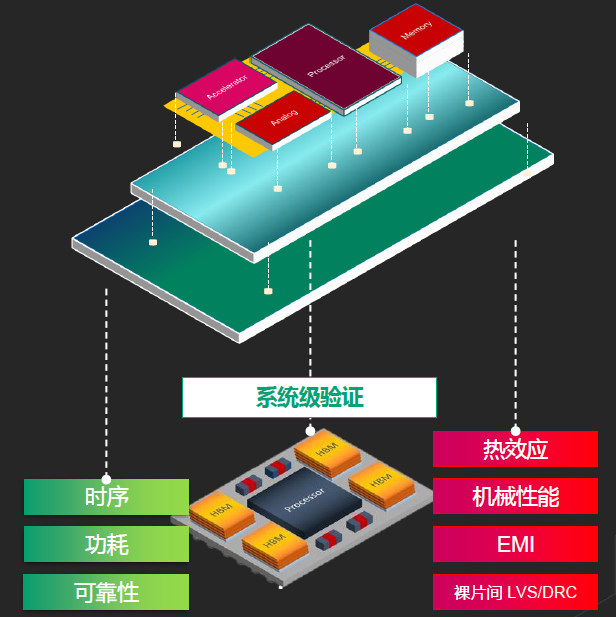

1) 3D-IC设计聚合与管理。包括:①裸片放置与Bump规划。②SoC和封装团队各自为战。③缺少代表多种技术的统一数据库。实际上,让数字工程师跟模拟工程师达成共识是很难的,因为他们没有共同的语言,共同的语言是统一的数据库,所以有聚合和管理上的挑战。

2) 额外的系统级验证。①系统级验证非常关键,要有跨芯片/Chiplet(小芯片)及封装的热分析。②3D STA(静态时序分析)的签核会有爆炸性的增加。③系统级的裸片间的连接验证。

为了解决上述痛点,Cadence公司不久前推出了一个全新的工具——Integrity 3D-IC。优势如下。

①集成了3D设计规划与物理实现,把所有的功能放在一起,已经成为一个平台。

②可以做早期3D电热、功耗和静态时序分析(STA)。实际上,从芯片到系统到最后的成型要有5个维度:光电磁力热,而Cadence所做的就是把这些整合起来。

③推出全新的3D IC平台,实现由系统来驱动的PPA(功耗、性能和面积)目标。

Integrity 3D-IC适合规模较大的芯片,例如CPU、GPU。

那么,不同的应用场景对于Integrity 3D-IC平台的需求有没有一些差异?刘淼解释道,对于存算一体化,有很多AI公司正在做。其目的是要让功耗不要消耗在传输上。存算一体就是把存储和运算要放在一起,但是,存储和运算放在一起面积会很大,可以把它们堆叠上去。在中国就有这类客户在跟Cadence合作。再例如,比特币矿机跟AI芯片很类似的,Cadence也在帮一些客户做3D堆叠,把存储尽量放在上面,运算放在下面。

另外一类客户是通讯客户。通讯的热点之一是带宽要足够,现在用得最多的是HBM,属于2.5D。这方面有一个典型的对比,一家客户以前是人工画HBM和SoC绕线,大概1人要花2周时间;如果用Integrity 3D-IC自动帮他绕线,连起来只用了2分钟!因为Integrity 3D-IC处理的都是百万级的计算,处理线非常简单,尽管人工看起来很多——有1000多条线,但是很快就完成了。所以技术的进步非常关键,弯道超车需要技术含量。

4 对比友商的优势

刘淼称,尽管有的友商的工具推得比Cadence早,但是不一定很成熟。而Cadence有平台和计算方面的优势。

① Cadence具有光、电、磁、力、热的分析工具,而友商没有这么全面,所以要和第三方合作。Cadence自己有数字部门和模拟部门,过去部门之间的整合花了很长时间,所以可能友商与不同公司的整合也会面临困难。

②Cadence Integrity 3D-IC的覆盖面更广。某友商当时重点做的一个技术是HBM,然而HBM技术含量相对较小,因为HBM是标准化的,SoC是非标准的;Cadence Integrity 3D-IC兼顾到了二者。

5 与中国客户共成长

Cadence在打造Integrity 3D-IC平台的过程中,有一部分想法是由中国团队提出来的。例如L1、L2缓存堆叠的技术。此前AMD有堆叠式L3缓存,但没有厂商在L1、L2上做。这就是Cadence员工跟中国一家客户吃饭聊出来的。Cadence中国进行了研发,相关员工和刘淼还申请了2个专利。

EDA工程师非常难得,大约10年才能成熟。Cadence在中国开设办公室已经接近30年,所以培养了很多超过10年的EDA工程师,甚至比美国的某些团队人数还要多,因此Cadence有能力更好地服务中国的设计业,帮助中国企业赶超世界。

评论