当人工智能遇到EDA,Cadence Cerebrus以机器学习提升EDA设计效能

随着算力的不断提升,人工智能的应用逐渐渗透到各个行业。作为人工智能芯片最关键的开发工具EDA,是否也会得到人工智能应用的助力从而更好地提升服务效率呢?答案自然是肯定的。随着半导体芯片设计的复杂度不断提升,以及芯片包含功能的日渐广泛,EDA的设计过程越来越需要借助人工智能来尽可能避免一些常见的设计误区,并借助大数据的优势来实现局部电路设计的最优化。在可以预见的未来,随着人工智能技术的不断引入,借助大数据和机器学习的优势,EDA软件将可以提供更高效更强大的设计辅助功能。

本文引用地址:https://www.eepw.com.cn/article/202110/428670.htm

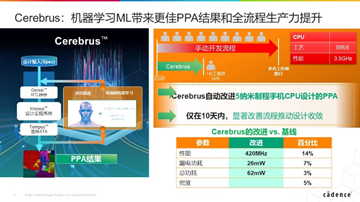

近日,楷登电子(Cadence)宣布推出 Cadence Cerebrus Intelligent Chip Explorer——首款创新的基于机器学习 (ML)的设计工具,可以扩展数字芯片设计流程并使之自动化,让客户能够高效达成要求严苛的芯片设计目标。Cerebrus 和 Cadence RTL-to-signoff 流程强强联合,为高阶工艺芯片设计师、CAD 团队和 IP 开发者提供支持,与人工方法相比,将工程生产力提高多达 10 倍,同时最多可将功耗、性能和面积 (PPA) 结果改善 20%。

如何界定Cerebrus与其他EDA工具的区别,Cadence公司数字与签核事业部产品工程资深群总监刘淼这样评价,Cerebrus已经超出了普通的EDA工具,它是凌驾于其他EDA工具之上的,它会用一种全新的全自动学习的工具凌驾于其他EDA工具之上,然后推出来更好结果的技能,这就是Cerebrus想要做的。

Cerebrus 采用可重复使用、可移植的增强学习模型,每次使用均可提高效率;与传统的人工设计过程相比,可实现更高效的本地和云计算资源管理,特别的,在多个工艺节点和多个终端应用中均可显著提高 PPA 和生产力,包括消费电子、超大规模计算、5G 通信、汽车电子和移动设备等。基于这些优势,Cerebrus 可以帮助使用者快速找到工程师可能不会尝试或探索的流程解决方案,提高 PPA 和生产力;同时允许将设计学习经验自动应用于未来的设计,缩短获得更好结果的时间;特别的,Cerebrus提供易于使用的界面和强大的用户管理工具,支持交互式结果分析和运行管理,以获得对设计指标的深入了解。此外,Cerebrus还可以让一位工程师同时为多个区块自动优化完整的 RTL-to-GDS 流程,提高整个设计团队的工作效率;另外,提供可扩展的本地或基于云的设计探索,实现更快的流程优化。针对可扩展性,刘淼指出,Cerebrus是基于可分布的、可扩展的计算解决方案,所以它可以用很多计算资源,无论是公有云或者企业的私有云都可以利用起来,利用可利用云的资源完成他的计算。

如果要以通俗点的话来描述Cerebrus,那就是结合Cadence服务过的各个客户的设计开发经验作为大数据,汇总反馈到Cadence这边通过机器学习,可以找到各个细节设计的最优解,然后再反馈并优化新的EDA工具中,最终帮助客户实现高效的芯片设计。而对Cerebrus的适用范围,刘淼则指出,无论是身处尚在温饱阶段挣扎的初级设计者,还是对接近小康的资深设计师,亦或是要考虑整个系统级芯片架构的大企业重点项目,都可以从Cerebrus中得到有益的帮助,并且可以大幅缩减从初级设计到资深设计所需要的时间和精力,并能有效提升大规模系统级芯片的设计效率。

随着 Cerebrus 加入到Cadence广泛的数字产品系列中,Cadence现在可以提供业界最先进的基于机器学习的数字全流程,从综合到实现和签核。这款新工具与多个领先云服务商合作启用了云计算服务,可利用高度可扩展的计算资源,快速满足包括消费电子、超大规模计算、5G 通信、汽车和移动等广泛市场的设计要求。

评论